뉴로모픽 시스템을 위한 간단한 SPICE 멤리스터 모델

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(https://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

A simple memristor model is proposed for the neuromorphic system in the Simulation Program for Integrated Circuits Emphasis (SPICE). The memristive I-V characteristics with different voltage and frequencies were analyzed. And with the model, we configured a learning and inference system with 4 by 4 memristor array to show the practical use of the model. We examined the applicability by configuring the simplest neuromorphic circuit. The total simulation time for the proposed model was 18% lesser than that for the one-memristor model. When compared with more memristor models in a circuit, the time became even shorter.

Keywords:

Memristor, RRAM, ReRAM, SPICE, Neuromorphic, Learning, Inference1. 서 론

최근 몇 년간, 인공지능은 딥러닝 기술의 획기적인 발전으로 인해 활발하게 연구되어 왔다. 딥러닝은 학습과 추론의 정확성을 더욱 향상시키는 방향으로 진전되어 왔다. 일반적으로 인공지능 학습은 소프트웨어를 통해 이루어지는데, 이 때 이루어지는 반복적인 연산이 큰 전력소모를 야기한다. 이러한 문제를 해결하기 위해 전자소자와 회로를 이용하는 하드웨어 학습에 대한 연구가 이루어졌다 [1-5].

학습에서 가중치를 설정하는 것이 중요한데 인공신경망을 구성하는 시냅스 소자의 전도도가 소프트웨어 학습에서의 가중치 역할을 한다. 그러므로, 시냅스 소자의 전도도는 변화 가능해야 한다. 학습에서 필수적인 기능인 가중치를 실현하기 위해 멤리스터, 이중게이트 MOSFET 등 여러 종류의 소자들이 사용되었다 [9-11]. 그 중에서도 멤리스터는 간단한 구조와 아날로그적 메모리 특성을 지녀 높은 밀도의 cross-point array를 가능하게 하므로 차세대 소자로 주목받고 있다 [11]. 그러나 멤리스터를 이용한 뉴로모픽 시스템은 global ion injection, random ion migration, stochastic conducting filament와 같은 문제점을 극복하기 위해 많은 연구가 진행중에 있다 [13,14].

학습을 위한 하드웨어 시스템은 크게 ANN(Artificial Neural Network)[6,7]방식과 SNN(Spiking Neural Network)[2,3,8]방식이 있다. ANN방식은 시냅스 소자에 특정한 신호를 크기, 빈도, 입력 시간에 따라 인가해주어 그 전도성을 변화시키는 방법이다. SNN방식은 인간의 뇌 신경을 모사하여 시냅스 소자의 전후로 인가되는 신호의 시간차에 따라 전도성 변화를 일으키는 방법이다.

하드웨어 시스템에서 학습은 현장(in-situ)학습과 현장 외(ex-situ) 학습이 있는데 현장방식은 하드웨어 외부의 도움없이 하드웨어 자체만 이용하여 학습을 하여 가중치를 변화시키는 방법을 말한다. 현장 외 방식은 각각의 시냅스 소자의 전도도를 변경시키 위해 가장 적절한 값을 소프트웨어를 이용하여 도출한 뒤 각 소자에 이식시켜주는 방식을 말한다.

멤리스터 cross point array는 크로스토크와 같은 문제가 있다[13,14]. 이로 인해, 대부분의 뉴로모픽 시스템 연구자들은 멤리스터의 특성이 통제가능한 시뮬레이션 툴을 이용하여 연구를 진행하고 있다. 이미 진행된 멤리스터 소자의 모델에 관한 연구[15-21]가 있다.

본 논문에서는 가장 SPICE시뮬레이션이 가능한 멤리스터 subcircuit 모델을 간단한 형태로 제시한다. 가장 간단한 뉴로모픽 회로를 구성하여 모델의 적용가능성을 확인할 수 있었다. 그리고 이 소자 모델을 이용하여 서로 다른 전압, 주파수를 가진 입력 신호와 다른 저항 값의 멤리스터 소자에 따른 시뮬레이션 실험의 결과를 통해 기존의 subcircuit 모델과 비교를 통해 시뮬레이션 시간의 단축도 보여준다.

2. 연구 방법

2.1 수학적 모델

수학적 모델은 HP Lab[22]의 TiO2 박막과 Pt 금속 전극으로 제작된 멤리스터에 기반한다. 멤리스터의 전류-전압 관계[15]는 기본적으로 다음과 같다.

| (1) |

| (2) |

D는 TiO2 층의 전체 길이이며, w는 도핑된 영역의 두께(혹은 형성된 CF의 길이)이다. RON과 ROFF는 w=0과 w=D일 때의 멤리스터의 저항값으로 제한된다.

2.2 SPICE Model

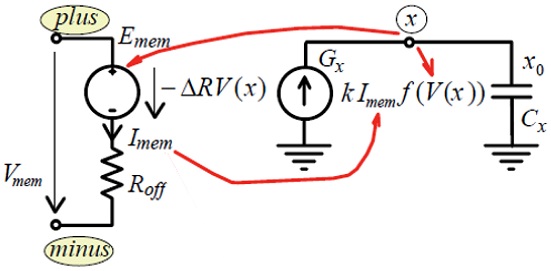

Fig. 1은 식(1), 식(2)를 바탕으로 구성한 전압원과 저항으로 이루어진 회로에 전압원의 하위회로(Sub-circuit)로 전류원과 커패시터를 이용하여 구현한 멤리스터 SPICE모델의 구조를 나타낸다. plus단과 minus 단에 전압이 인가되면 Imem이 흐르고 이 전류값이 하위 회로에 흐르게 된다. 이 전류는 커패시터를 충전시키고 이 때 충전된 전압이 다시 전압원의 저항을 바꾸어 멤리스터의 전도도를 변화시킨다. 멤리스터 저항에 대한 식[15]은 수식 (3)과 같다.

| (3) |

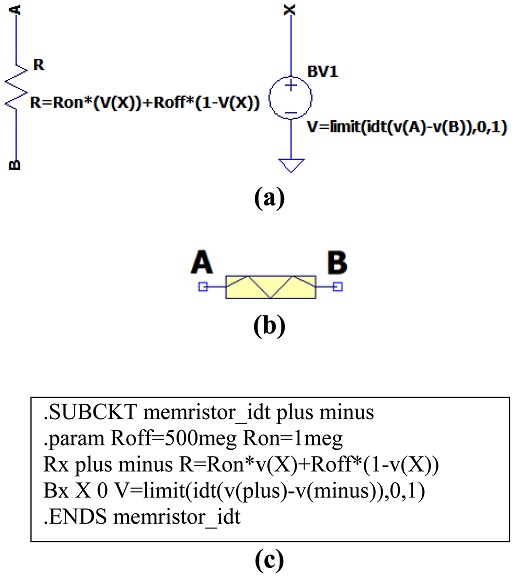

Fig. 2(a)는 SPICE의 여러 기능들을 이용한 SPICE 모델이며, Fig. 2(b)는 해당 모델의 심볼을 나타낸다. 넓이w가 가해진 전압의 이력에 따라 바뀌는 것과 같이, Fig. 2(b)에서 x에서의 전압은 멤리스터 모델의 양단 A, B에 가해진 전압의 적분으로 표현할 수 있으며, w는 x의 전압값에 대응된다고 할 수 있다. 이 모델을 구현하기 위해 arbitrary behavior voltage source를 이용하였으며, “limit”기능과 “integral”기능을 이용하였다. A, B 양단에 전압이 인가되면 적분기능을 가진 “idt”함수는 양단 전압을 적분한다. 여기서 적분 값은 식 (1)의 x 와 같은 역할을 한다. “limit”기능을 활용하여, w = 0과 w = D일 때의 상태를 표현하였다.

3. 결과 및 고찰

3.1 SPICE 모델 분석

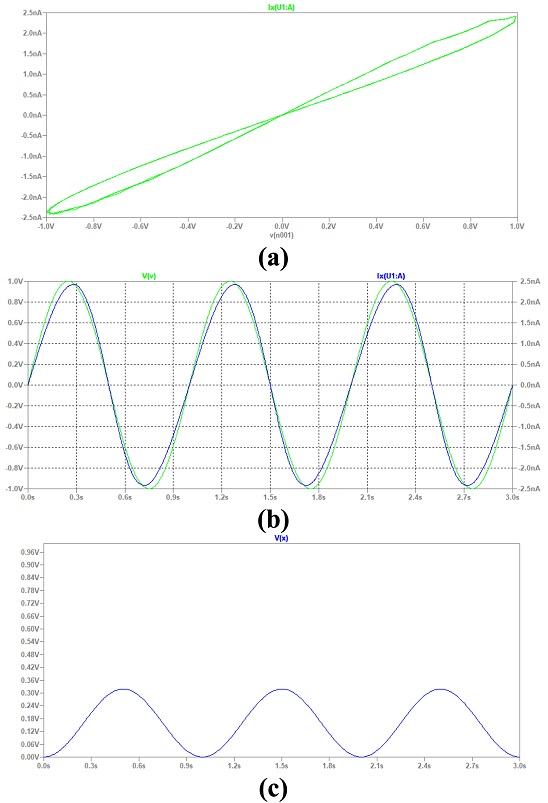

SPICE모델은 [15]와 같은 방법으로 분석되었다. Fig. 3은 멤리스터의 양단에 사인파를 인가하였을 때의 I-V 특성 그래프를 나타낸다. 이 때, 입력전압은 VAB=sin(2πt) 이며, RON= 1MΩ, ROFF= 500 MΩ이다. Fig. 3(a)는 인가된 전압 신호에 대한 전류의 크기를 나타낸다. 특성곡선은 멤리스터가 이력을 기억함에 따라 히스테리시스를 가지는 형태로 나타나게 된다. Fig. 3(b)는 시간에 따른 입력전압과 출력전류를 나타낸다. 입력전압에 의해 멤리스터의 전도도가 변화하기 때문에 출력전류는 Sine함수가 약간 왜곡된 형태의 파형을 보인다. Fig. 3(c)는 Fig. 2(a)에서 A-B의 적분 값인 X노드에서의 전압을 나타낸다. 이것은 실제 멤리스터 모델에서 전도 필라멘트의 길이에 대응될 수 있다. 의 최댓값은 330 mV이며 이 때 V(X)는 SPICE의 “limit”기능으로 인해 1V이상의 값은 가지지 못하도록 제한되어 있으나 Fig. 3에서 그 영향은 없다.

VAB=sin(2πt), RON=1 MΩ, ROFF= 500 MΩ (a) I-V characteristic, (b)The voltage across the model and the current through it, (c) (c) V(X): The voltage of node X at Fig. 2.

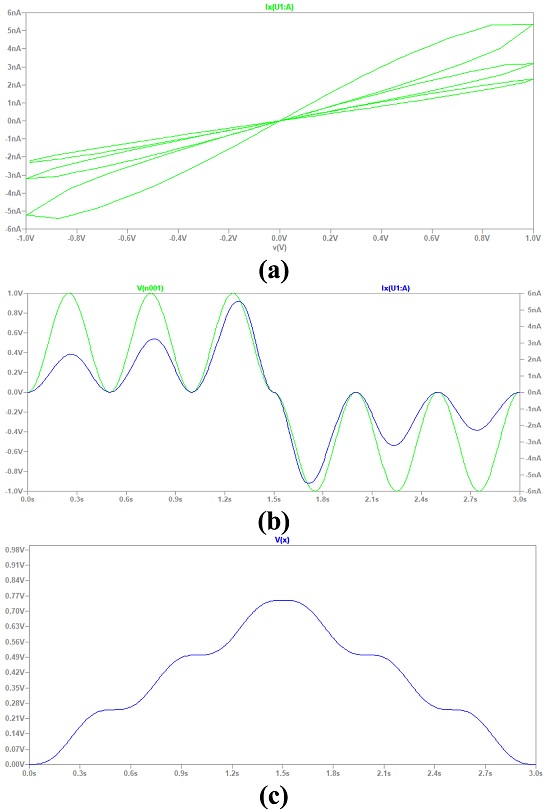

Fig. 4는 RON=1MΩ, ROFF= 500MΩ에서 입력전압이 VAB=±(sin2πt)2일 때를 분석한 결과이다. VAB= ±(sin2πt)2는 같은 크기의 전압이 연속해서 입력이 되므로 입력에 따른 멤리스터의 전도도 변화를 더 직관적으로 알아볼 수 있다. Fig. 4(b)에서 멤리스터 소자에 같은 크기의 전압이 반복적으로 인가되는 경우 그 소자를 흐르는 전류크기가 점점 증가하는 것을 볼 수 있다. Fig. 4(a)는 전압이 인가되었을 때 시간에 따른 전류의 크기를 나타낸다. 이 그래프를 통해서도 동일한 반복적 입력 전압에 따른 멤리스터 모델의 전도도 변화를 알 수 있으며, 입력신호가 반복 될수록 전도도가 커지며 히스테리시스 또한 커진다는 것을 확인할 수 있다.

VAB= ±(sin2πt)2, RON= 1 MΩ, ROFF= 500 MΩ (a) I-V characteristic, (b) The voltage across the model and the current through it, (c) V(X): The voltage of node X at Fig. 2.

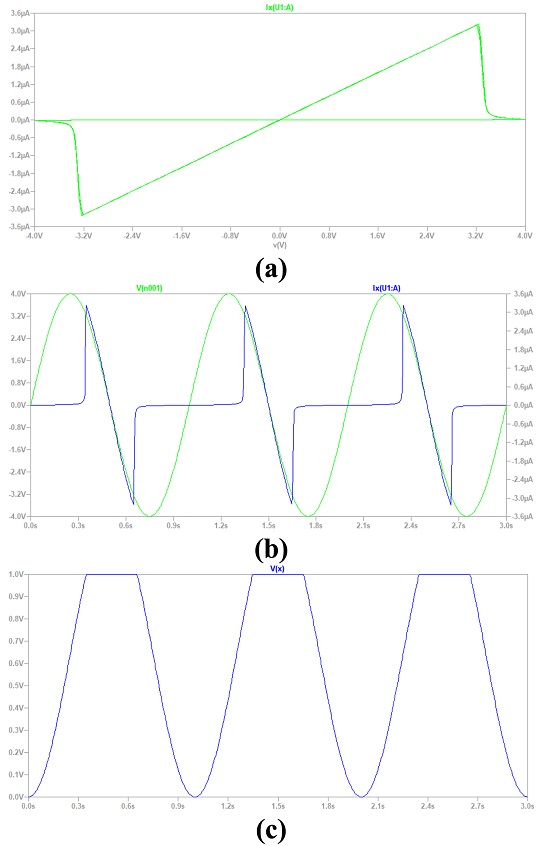

Fig. 5는 VAB=4sin(2πt), RON=1MΩ, ROFF = 500 MΩ일 때를 측정한 그래프이다. 이 때의 전류 그래프는 Fig. 3과 Fig. 4의 그래프보다 훨씬 더 일그러진 파형을 보여준다. Fig. 5(c)의 V(X)의 경우 0과 1사이의 값으로 제한되는 “limit”에 의해 그 값이 1에 도달했을 때 그 값이 유지되는 것을 확인할 수 있다. 이러한 현상은 실제의 멤리스터에서 이온 이동(Ion Migration)으로 인한 전도 필라멘트의 형성으로 양 전극이 이어졌을 때, 인가된 전압이 필라멘트의 형성보다 전자의 드리프트에 더 큰 영향을 미치는 상태를 모사한다. VAB= sin(2πt)의 전압을 인가하였을 때, 멤리스터 소자를 통해 흐르는 전류는 Fig. 3, Fig. 4에서 각각 최대 2.5 nA, 5.5 nA임에 비해 VAB= 4sin(2πt)를 인가한 Fig. 5는 3.3 uA로 훨씬 크게 나타난다.

VAB= 4sin(2πt), RON = 1MΩ, ROFF= 500 MΩ (a) I-V characteristic, (b) The voltage across the model and the current through it, (c) V(X): The voltage of node X at Fig. 2.

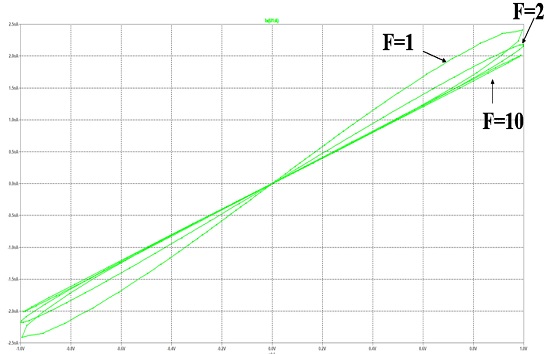

Fig. 6은 같은 크기의 서로 다른 주파수 VAB= sin(2πt), sin(4πt), sin(20πt)가 인가되었을 때 I-V특성곡선을 나타낸다. 주파수가 커짐에 따라 전류의 최댓값은 줄어들었고, 히스테리시스 또한 줄어들었다.

3.2 멤리스터 모델의 적용

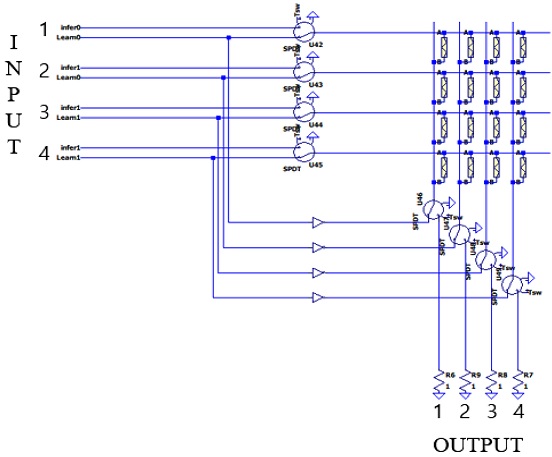

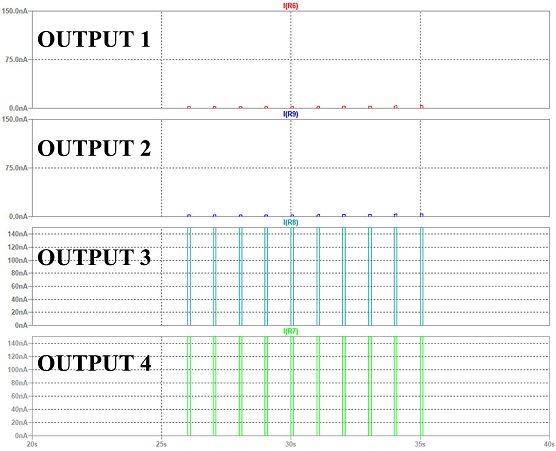

멤리스터 모델이 neuromorphic 회로 시스템에 적용가능한지 확인해보기 위해 4개의 입력단과 4 "~ 4멤리스터 어레이를 가지는 Fig. 7과 같은 회로 시스템을 구성하였다. 회로구성은 전압원과 3로 스위치(SPDT Switch), 인버터, 멤리스터로 구성되었다. 시스템은 첫 번째 단계와 두 번째 단계로 나뉘는데 첫 번째 단계에서는 큰 전압을 인가하여 전도도의 변화를 일으키고, 두 번째 단계에서는 전도도 변화를 일으키지 않을 정도의 전압을 인가하여 멤리스터 어레이의 전도도 변화를 확인하였다. 25초를 기점으로 이 전을 첫 번째 단계로 이용을 하고, 이 후는 두 번째 단계로 이용하였다. 첫 번째 단계에서는 “Learn”을 통해 신호가 입력이 주었고 두 번째 단계에서는 “Infer”를 통해 입력을 주었다. 각 단계의 입력과 출력은 1, 2, 3, 4개의 단으로 구성되어 있다. 단계가 바뀔 때, 3로 스위치를 통해 경로가 결정된다. 스위치는 25초에 경로가 변경되도록 설정되었다.

첫 번째 단계에서는 “Learn1”의 입력단으로 Von=0.5V, Trise=Tfall=0.001sec, Ton=0.5sec, Tperiod=1sec의 사각파가 3회 입력되고, “Learn0”의 입력단으로는 Voff=0V가 입력된다. Fig. 7의 경우, 입력단의 1, 2는 “Learn0”, 3, 4는 “Learn1”을 입력으로 한다. 학습 단계에서 스위치를 통한 경로는 Learn 신호가 멤리스터의 A로 입력이 되며, 인버터를 통해 신호가 반전되어 멤리스터의 B로 입력이 되어 멤리스터의 전도도 변화를 일으킨다.

25초 후 스위치에 의해 회로의 경로가 달라지게 되며 두 번째 단계가 시작되고 “Infer” 전압이 인가된다. 이 때, 전류는 입력 전압원으로부터 시작되어 멤리스터를 지나 출력의 저항쪽으로 흐른다. 두 번째 단계에서는 “Infer1”을 통해 Von= 0.05V, Trise= Tfall= 0.001sec, Ton= 0.1sec, Tperiod= 1sec의 사각파가 10회 인가되었다. “Infer0”을 통해서는 Voff=0V가 인가되었다. 입력 1에는 “Infer0”, 입력 2, 3, 4는 “Infer1”을 인가하여 첫 번째 단계에서 입력을 통해 어레이 각각의 전도도가 서로 다르게 변화한 것을 확인 할 수 있었다.

이 결과는 Fig. 8에서 나타났다. 첫 번째 단계에서 입력 3, 4에 큰 전압을 걸어 주었으므로 출력 3, 4으로 흐르는 전류가 출력 1, 2로 흐르는 전류에 비해 상당히 크게 나타남을 확인할 수 있었다. 이러한 시스템은 멤리스터 어레이가 인가되는 전압에 따라 각각 전도도의 변화가 다르게 나타나며 과거의 이력이 저장 가능하다는 것을 보여준다.

3.3 SPICE 시뮬레이션 경과시간

마지막으로, 1sec동안 V =A0sinωt(A0= 1, ω = 100 k/2π일 때)의 전압을 인가하여 시뮬레이션에 소모된 시간을 측정하여 비교하였다. 시뮬레이션은 같은 조건에서 5회 반복하여 평균을 내어 구하였다. 먼저, Zdeněk BIOLEK [15]에서 사용된 모델을 이용했을 때, 평균 22.37초가 소요되었다. 두 번째로, 이 모델에서 실험에 필요하지 않은 자계와 전하량에 대한 코드를 제외하고 시뮬레이션을 진행하였고, 이 때 소요된 시간은 평균 20.25초로 감소하였다. 세 번째로 이 논문에서 제시된 모델을 사용하여 시뮬레이션을 진행하였을 때, 소요된 시간은 평균 18.34초로 가장 빠르게 시뮬레이션이 동작함을 확인할 수 있었다. 추가적으로, 더 많은 멤리스터가 있을 때의 시뮬레이션에 걸리는 시간을 확인해보기 위하여 간단히 멤리스터 모델 5개를 병렬로 연결하여 시뮬레이션 시 소모되는 시간을 측정하였다. Zdeněk BIOLEK 모델의 경우 평균 47.14초, 수정된 모델의 경우 평균 36.44초, 본 논문에 제시된 모델의 경우 36.62초로 측정이 되었다. 시뮬레이션에 사용되는 멤리스터의 모델의 개수가 늘어남에 따라 모델에 따라 시뮬레이션에 소모되는 시간의 격차가 더 크게 나타나는 것을 확인할 수 있었다.

4. 결 론

이 연구에서는 기존의 멤리스터 모델에 비해 더 간단한 SPICE 모델을 제안하였다. 가장 간단한 뉴로모픽 회로를 구성하여 모델의 적용가능성을 확인할 수 있었다. SPICE의 여러 기능들을 이용하여 종전의 멤리스터 코드들에 비해 더 짧은 코드를 이용하여 동일한 결과를 가질 수 있었다. 이 멤리스터 모델을 통해 여러 전압신호와 주파수에 대한 I-V특성을 확인할 수 있었다. 이 모델을 이용하여 간단한 뉴로모픽 회로에 적용하여 멤리스터 모델의 전도도 변화에 따라 동일한 입력에 대한 다른 출력을 나타내는 것을 확인하였다. 이전의 멤리스터 SPICE 모델과 시뮬레이션에 소비되는 시간을 비교한 결과 18%정도의 시간을 절약할 수 있었다. 이에 따라 더 많은 계산이 필요할 경우 시간적 차이는 더 커짐도 확인하였다.

Acknowledgments

본 연구는 대한민국 교육부의 재원으로 BK21 4단계 사업(4199990113966)과 정부의 재원으로 한국연구재단의 지원(No. 2020R1I1A3A04037962), 그리고 산업통상자원부 ‘산업전문인력역량강화사업’의 재원으로 한국산업기술진흥원(KIAT)의 지원(2021년 첨단센서 전문인력 양성사업, 과제번호 : P0001018)을 받아 수행된 연구임.

REFERENCES

-

M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev, and D. B. Strukov, “Training and operation of an integrated neuromorphic network based on metaloxide memristors”, Nature, Vol. 521, pp. 61-64, 2015.

[https://doi.org/10.1038/nature14441]

-

G. Kim, K. Kim, S. Choi, H. J. Jang, and S. O. Jung, “Area- and energy-efficient STDP learning algorithm for spiking neural network SoC”, IEEE Access, Vol. 8, pp. 216922-216932, 2020.

[https://doi.org/10.1109/ACCESS.2020.3041946]

-

G. K. Chen, R. Kumar, H. E. Sumbul, P. C. Knag, and R. K. Krishnamurthy, “A 4096-Neuron 1M-Synapse 3.8-pJ/SOP spiking neural network with on-chip STDP learning and sparse weights in 10-nm FinFET CMOS”, IEEE J. Solid-State Circuits., Vol. 54, No. 4, pp. 992-1002, 2019.

[https://doi.org/10.1109/JSSC.2018.2884901]

-

Y. S. Yang and Y. Kim, "Recent trend of neuromorphic computing hardware: Intel's neuromorphic system perspective", 2020 Int. SoC Des. Conf. (ISOCC), pp. 218-219, Yeosu, South Korea, 2020.

[https://doi.org/10.1109/ISOCC50952.2020.9332961]

-

M. Chu, B. Kim, S. Park, H. Hwang, M. Jeon, B. H. Lee, and B. G. Lee, “Neuromorphic hardware system for visual pattern recognition with memristor array and CMOS neuron”, IEEE Trans. Ind. Electron., Vol. 62, No. 4, pp. 2410-2419, 2015.

[https://doi.org/10.1109/TIE.2014.2356439]

-

J. Misra, I. Saha, “Artificial neural networks in hardware: A survey of two decades of progress”, Neurocomputing, Vol. 74, No. 1-3, pp. 239-255, 2010.

[https://doi.org/10.1016/j.neucom.2010.03.021]

-

M. Kimura, R. Sumida, A. Kurasaki, T. Imai, Y. Takishita, and Y. Nakashima, “Amorphous metal oxide semiconductor thin film, analog memristor, and autonomous local learning for neuromorphic systems”, Sci. Rep., Vol. 11, No.1, pp. 1-7, 2021.

[https://doi.org/10.1038/s41598-020-79806-w]

-

J. J. Lee, J. Park, M. W. Kwon, S. Hwang, H. Kim, and B. G. Park, “Integrated neuron circuit for implementing neuromorphic system with synaptic device”, Solid State Electron., Vol. 140, pp. 34-40, 2018.

[https://doi.org/10.1016/j.sse.2017.10.012]

-

S. H. Lee, H. L. Park, M. H. Kim, M. H. Kim, B. G. Park, and S. D. Lee, “Realization of Biomimetic Synaptic Functions in a One-Cell Organic Resistive Switching Device Using the Diffusive Parameter of Conductive Filaments”, ACS Appl. Mater. Interfaces., Vol. 12, No. 46, pp. 51719−51728, 2020

[https://doi.org/10.1021/acsami.0c15519]

-

H. Kim, S. Cho, M. C. Sun, J. Park, S. Hwang, and B. G. Park, “Simulation Study on Silicon-Based Floating Body Synaptic Transistor with Short- and Long-Term Memory Functions and Its Spike Timing-Dependent Plasticity”, J. Semicond. Technol. Sci., Vol. 16, No. 5, pp. 657-663, 2016.

[https://doi.org/10.5573/JSTS.2016.16.5.657]

-

S. Choi, S. H. Tan, Z. Li, Y. Kim, C. Choi, P. Y. Chen, H. Chen, S. Yu, and J. Kim, “SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations”, Nat. Mater., Vol. 17, No. 4, pp. 335-340, 2018.

[https://doi.org/10.1038/s41563-017-0001-5]

-

Y. Sun, C. Song, J. Yin, X. Chen, Q. Wan, F. Zeng, and F. Pan, “Guiding the Growth of a Conductive Filament by Nanoindentation To Improve Resistive Switching”, ACS Appl. Mater. Interfaces, Vol. 9, No. 39, pp. 34064–34070. 2017.

[https://doi.org/10.1021/acsami.7b09710]

-

F. Gül, “Addressing the sneak-path problem in crossbar RRAM devices using memristor-based one Schottky diode-one resistor array”, Results Phys., Vol. 12, pp. 1091-1096, 2019.

[https://doi.org/10.1016/j.rinp.2018.12.092]

-

L. Shi, G. Zheng, B. Tian, B. Dkhil, and C. Duan, “Research progress on solutions to the sneak path issue in memristor crossbar arrays”, Nanoscale Adv., Vol. 2, No. 5, pp. 1811-1827, 2020.

[https://doi.org/10.1039/D0NA00100G]

- Z. Biolek, D. Biolek, and V. Biolkova, “SPICE model of memristor with nonlinear dopant drift”, Radioengeering, Vol. 18, No. 2, 2009.

-

D. Batas and H. Fiedler, “A memristor SPICE implementation and a new approach for magnetic flux-controlled memristor modeling”, IEEE Trans. Nanotechno., Vol. 10, No. 2, pp. 250-255, 2011.

[https://doi.org/10.1109/TNANO.2009.2038051]

-

M. J. Sharifi and Y. M. Banadaki, “General spice models for memristor and application to circuit simulation of memristor-based synapses and memory cells”, J. Circuits Syst. Comput., Vol. 19, No. 2, pp. 407-424, 2010.

[https://doi.org/10.1142/S0218126610006141]

-

Á. Rak, and G. Cserey, “Macromodeling of the memristor in SPICE”, IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., Vol. 29, No. 4, pp.632-636, 2010.

[https://doi.org/10.1109/TCAD.2010.2042900]

-

H. Abdalla and M. D. Pickett, “SPICE modeling of memristors”, 2011 IEEE Int. Symp. Circuits and Syst. (ISCAS), pp. 1832-1835, Rio de Janeiro, Brazil, 2011.

[https://doi.org/10.1109/ISCAS.2011.5937942]

-

A. F. Adzmi, A. Nasrudin, W. F. H. Abdullah, and S. H. Herman, “Memristor Spice model for designing analog circuit”, 2012 IEEE Stud. Conf. Res. Dev. (SCOReD), pp. 78-83, Pulau Pinang, Malaysia, 2012.

[https://doi.org/10.1109/SCOReD.2012.6518615]

-

C. Yakopcic, T. M. Taha, G. Subramanyam, and R. E. Pino, “Memristor SPICE model and crossbar simulation based on devices with nanosecond switching time”, The 2013 Int. Jt. Conf. Neural Netw. (IJCNN), pp. 1-7, Dallas, USA, 2013.

[https://doi.org/10.1109/IJCNN.2013.6706773]

-

D. B. Strukov, G. S. Snider, D. R. Stewart and R. S. Williams, “The missing memristor found”, Nature, Vol. 453, No. 7191, pp. 80–83, 2008.

[https://doi.org/10.1038/nature06932]