바이오 센서 적용을 위한 수직형 이중게이트 InGaAs TFET의 게이트 열화 현상 분석

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(https://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

In this study, we have fabricated and characterized vertical double-gate (DG) InGaAs tunnel field-effect-transistors (TFETs) with Al2O3/HfO2 = 1/5 nm bi-layer gate dielectric by employing a top-down approach. The device exhibited excellent characteristics including a minimum subthreshold swing of 60 mV/decade, a maximum transconductance of 141 μS/μm, and an on/off current ratio of over 103 at 20oC. Although the TFETs were fabricated using a dry etch-based top-down approach, the values of DIBL and hysteresis were as low as 40mV/V and below 10mV, respectively. By evaluating the effects of constant voltage and hot carrier injection stress on the vertical DG InGaAs TFET, we have identified the dominant charge trapping mechanism in TFETs.

Keywords:

Bio sensor, Tunneling, TFET, InGaAs, Sub-thermal subthreshold swing, Reliability, CVS, HCI1. 서 론

지난 수십 년 동안 눈에 보이지 않는 생물학적 위험 요인들이 발생해왔으며, 최근 코로나 바이러스를 포함하여 흑사병, 독감 등의 고 전염성 바이러스들은 인간 생태계에 깊숙이 침투하여, 우리의 삶을 불안정하게 만들고 있다. 이와 동시에, 북한을 포함한 세계 각국에서는 전쟁을 대비하여 생물화학무기를 개발중이며, 해당 무기는 민간인들에게도 심각한 피해를 발생시키고 포격 지역에 회복하기 어려운 중장기적인 피해를 야기하는 특징을 갖는다. 따라서, 이러한 생물학적 위험 요인들을 탐지하는 기술은 인간 생태계 유지를 위해 필수적인 사항이 되었다.

군수에서 활용되는 생물학적 요인의 탐지뿐 아니라, 질병의 검진, 기상 관측 등에서의 활용을 위해서 고민감도를 가지는 전계 효과 트랜지스터 (Field-effect-transistor, FET) 기반 바이오센서에 대한 연구가 세계적으로 진행되고 있다 [1-4]. 수 십 년 동안, 실리콘 (Si) 기반 상보형 금속 산화물 반도체 (Complementary metal–oxide–semiconductor, CMOS)의 구조적 혁신 및 소자 소형화를 통해 바이오 센서의 성능과 집적도가 크게 발전하였지만, 금속 산화물 반도체 전계 효과 트랜지스터 (Metal-oxide-semiconductor field-effect-transistor, MOSFETs)의 동작 원리에 의한 제한으로 인해 다음 두 가지 한계점이 존재한다. ① 상온에서 문턱 전압 이하 스윙 (Subthreshold Swing)의 최소값이 60 mV/decade이며, 이로 인해 공급 전압 (Supply voltage, VDD)을 줄이는 데 한계가 있다. ② 소자의 소형화로 인해 단채널 효과 (Short channel effect, SCE)가 발생하여 회로 설계의 복잡도를 증가시킨다.

이러한 문제를 해결할 수 있는 반도체 소자로써, 터널 전계 효과 트랜지스터 (TFETs)가 고려되고 있다. 열전자 방출 (Thermionic emission, TE)에 의해 전도대역의 전자가 이동함으로써 전류가 생성되는 MOSFET과는 다르게, TFET은 가전자대역에서 전도대역으로의 터널링 (Band-to-band-tunneling, BTBT)을 통해 전류가 발생되기 때문에, 스윙을 60 mV/decade 이하로 감소시키고, VDD를 0.3 V이하로 낮춤으로써 바이오 센서에 활용하였을 때, 모듈의 소비 전력을 최소화 수 있다는 특징이 있다 [5,6]. 또한, 주목할 만한 점은, 동작 전류가 소스 (Source)와 채널 (Channel) 사이에 발생하는 터널링에 의해 제어되기 때문에, SCE에서 자유로울 수 있다는 것이다 [7, 8].

FET 기반 바이오센서의 실용화를 위해서는 우수한 소자 특성과 동시에, 외부 자극에 의한 특성 변화 및 소자의 수명을 통칭하는 소자의 신뢰성이 중요한 요소이다. 소자의 신뢰성을 평가할 수 있는 지표는 문턱 전압 (Threshold voltage, VT), 동작 전류, 스윙, 트랜스컨덕턴스 (Trans-conductance, gm) 등이 있으며, 오랜 시간 동작 시에 발생하는 해당 지표들의 변화는 센서의 오동작 또는 고장으로 이어지게 된다 [7,9,10].

본 논문에서는 Si 대비 높은 동작 전류 (ION)를 얻을 수 있는 InGaAs를 채널 물질로 사용하여, 상온에서 최소 스윙 (Smin) = 60 mV/decade, 동작 전류 (ION) = 7.52 mA/mm, 최대 트랜스컨덕턴스 (gm_max) = 141 mS/mm 특성을 가지는 수직형 이중게이트 InGaAs TFET (Vertical Double-Gate (DG) InGaAs TFETs)을 하향식 공정 방식으로 제작하고, constant voltage stress (CVS) 및 hot carrier injection (HCI)에 의한 핵심 지표의 변화를 관측함으로써, 지배적인 트래핑 매커니즘을 규명하였다.

2. 소자 공정

수직형 이중게이트 InGaAs TFET 제작을 위한 에피층은 Semi-insulation InP 기판 상에 분자-빔-에피택시 (Molecular beam epitaxy, MBE) 방식으로 성장되었다. 에피층은 50 nm 두께 n+In0.53Ga0.47As (Si 도핑, 5 × 1019 cm-3), 30 nm 두께 n+ In0.53Ga0.47As 드레인 영역(Si 도핑, 1 × 1017 cm-3), 90 nm 두께 진성 In0.53Ga0.47As 채널 영역, 10 nm 두께 진성 In0.8Ga0.2As 포켓 영역, 300 nm 두께 p+ In0.53Ga0.47As 소스 영역(Be 도핑, 5 × 1019 cm-3) 및 300 nm 두께 진성 In0.53Al0.48As 완충층으로 구성된다.

소자 제작은 본 연구실에서 기 발표된 논문과 유사한 방식으로 진행되었는데, 식각된 InGaAs 측벽과 고 유전율 게이트 절연막 (High-k) 사이의 dangling bond에 의한 trap을 완화시키기 위해 절연막 증착 전에 21% 황화 암모늄 ((NH4)2S) 용액에 10분간 처리한 후 원자층 증착 장비 (Atomic-layer-deposition, ALD)를 이용하여 Al2O3/HfO2 = 1/5 nm의 이중 게이트 절연막을 형성하였다 [11].

3. 결과 및 고찰

3.1 제작된 수직형 이중게이트 InGaAs TFET의 DC 특성

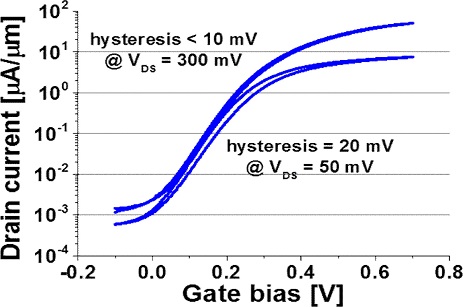

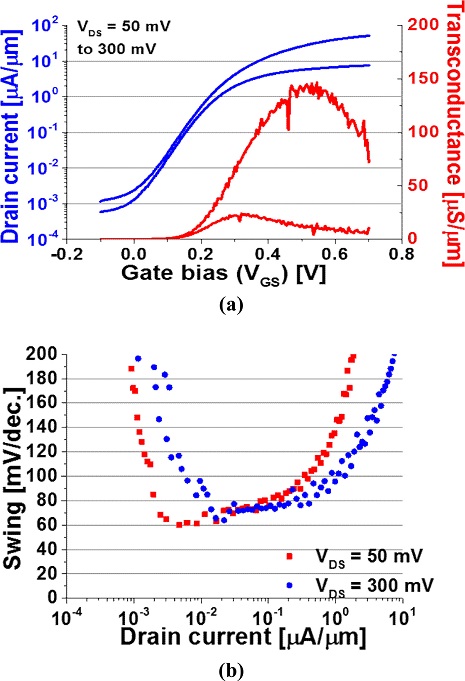

Fig. 1은 제작된 수직형 이중게이트 InGaAs TFET 소자의 상온에서의 문턱전압이하 (Subthreshold) 특성을 보여준다. Fig. 1 (b)에서 볼 수 있듯이, 제작된 소자는 drain-to-source voltage (VDS) = 50 mV 일 때, 60 mV/decade의 스윙 특성을 보여주었는데, 이는 MOSFET 소자의 이론적 한계수치와 동일하다. 또한, VDS = 300 mV에서 ION = 7.52 mA/mm (ION = ID @ VGS = VT + 0.2 V), gm_max = 141 mS/mm, 드레인 유도 장벽 감소 (Drain-induced-barrier-lowering, DIBL) = 40 mV/V의 특성을 보였으며, 특히 VDD = 0.3 V 일 때 (VDS = DVGS = 0.3 V), ON/OFF 전류 비율이 103 이상의 값을 보였다. Fig. 2는 VDS = 50, 300 mV 일 때의 이력 현상 (hysteresis)을 보여주고 있는데, 그 값이 20 mV, 10 mV 이하로 굉장히 작은 값을 나타내었다.

(a) Subthreshold characteristics and (b) subthreshold swing vs. drain current of the fabricated vertical DG InGaAs TFETs.

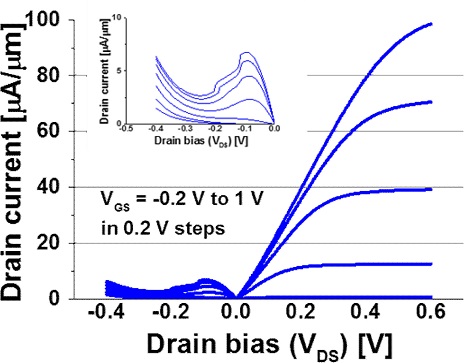

정방향 전압과, 역방향 전압에서의 소자 출력 (Output) 특성을 Fig. 3에 표현하였다. 정방향 전압에서는 BTBT에 의해 전류가 발생하고, VDS 가 증가함에 따라 ID가 포화되는 특성을 보인다. 이는 게이트 길이 (LG)가 100 nm로 매우 작음에도 SCE가 작용하지 않음을 의미한다. 삽화와 같이, 제작된 수직형 이중게이트 InGaAs TFET 소자는 역방향 전압에서 부성 미분 저항 (Negative differential resistance, NDR) 특성을 보여주었는데, 이는 전류 발생원이 BTBT에서 TE로 바뀌면서 발생되는 현상이다.

3.2 CVS 및 HCI에 의한 게이트 노화 현상 평가

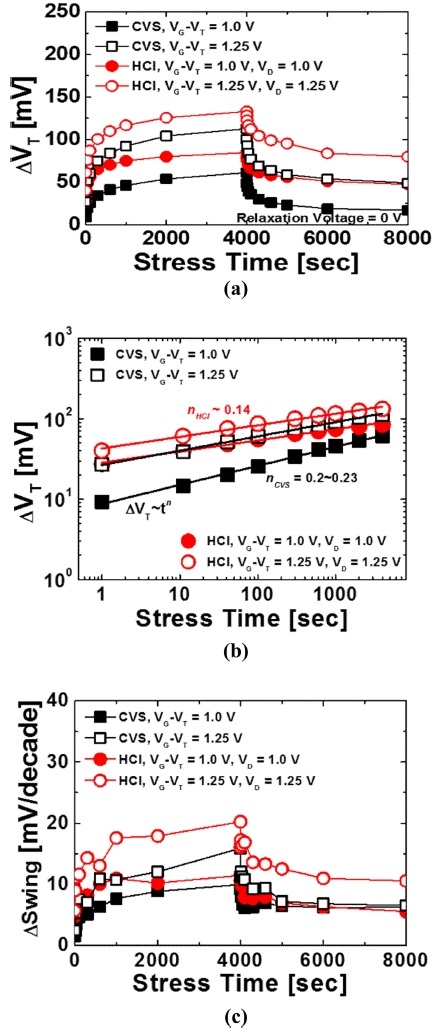

Fig. 4는 고 유전율 게이트 절연막을 사용하여 제작된 수직형 이중게이트 InGaAs TFET 소자의 CVS 및 HCI 스트레스에 따른 특성 변화를 보여준다. 1/10/100/300/ 500/1000/2000/4000 초의 스트레스 인가 후 0 V의 회복 전압을 동일한 시간 간격으로 인가하여 특성 변화를 관찰하였다. CVS 조건에서 캐리어 (carrier)는 매우 짧은 스트레스 시간 동안, 계면에 가까운 게이트 산화물의 얕은 부분 (fast trap)에 쉽게 트래핑 되며, 급격한 특성 변화를 유발시킨다. 그리고 스트레스 시간이 길어짐에 따라 깊은 부분 (slow trap)에 트래핑이 발생하고 특성을 천천히 변화시킨다 (Fig. 4 (a)) [12-14]. HCI 조건에서는 게이트 산화물 – 채널 사이의 트랩뿐 아니라, FET의 터널 접합 부분의 트랩의 영향이 누적되어 나타나는데, 이는 TFET의 터널링 접합 부분 (소스-채널 접합)의 게이트 산화물 – 채널의 계면 트랩에 기인한다 [15,16]. 결과적으로, HCI 스트레스 동안 VT 열화는 터널링 접합 부분의 수직/수평 전기장에 의한 영구적 손상과, 게이트 전압에 의해 형성되는 수평 전기장에 의한 게이트 산화물 및 계면의 결함으로 발생하는 전하 주입의 복수 원인해 인해 발생한다. VT 변화의 시간 의존성은, DVT ~ tn의 멱함수로 표현 될 수 있는데, 종속도를 나타내는 지수 n의 값이 HCI 조건에서 0.14인 반면, CVS 조건에서는 0.2에서 0.23 사이임을 확인 할 수 있다 (Fig. 4 (b)). 이는 CVS 조건과 HCI 조건에서의 지배적인 전하 트래핑 매커니즘의 차이가 있음을 의미하는데, HCI 조건에서 터널링 접합 부분의 결함이 크게 발생됨을 알 수 있다. 스트레스 시간에 따른 스윙 열화 양상을 Fig. 4 (c)에 나타내었다. 스트레스에 의해 열화된 스윙은 회복을 통해 어느정도 회복되지만, 게이트 산화물의 영구적 손상으로 인해 완전히 회복되지 않는 양상을 보였다.

4. 결 론

본 연구에서는 하향식 공정 방식으로 수직형 이중게이트 InGaAs TFET을 제작하고, CVS, HCI 스트레스에 대한 트랩 거동 양상을 분석하였다. 제작된 TFET 소자는 MOSFET의 열적 한계 스윙인 60 mV/decade의 최소 문턱전압이하 스윙과 141 mS/mm의 높은 트랜스컨덕턴스 값을 보여주었다. 우수한 특성을 가지는 TFET 소자에 CVS 및 HCI 스트레스를 인가하고, TFET 동작 시 터널링 접합 부분의 계면 트래핑이 주요한 특성 열화 요인임을 규명하였다.

Acknowledgments

이 논문은 2021 년도 정부 (과학기술정보통신부)의 재원으로 한국연구재단-나노·소재기술개발사업의 지원을 받아 수행된 연구임 (NRF-2017M3A7B4049517).

REFERENCES

-

X. P. A. Gao, G. Zheng, and C. M. Lieber, “Subthreshold Regime has the Optimal Sensitivity for Nanowire FET Biosensors”, Nano Lett., Vol. 10, No. 2, pp. 547-552, 2010.

[https://doi.org/10.1021/nl9034219]

-

A. Gao, N. Lu, P. Dai, T. Li, H. Pei, X. Gao, Y. Gong, Y. Wang, and C. Fan, “Silicon-Nanowire-Based CMOS-Compatible Field-Effect Transistor Nanosensors for Ultrasensitive Electrical Detection of Nucleic Acids”, Nano Lett., Vol. 11, No. 9, pp. 3974-3978, 2011.

[https://doi.org/10.1021/nl202303y]

-

G. Zheng, F. Patolsky, Y. Cui, W. U. Wang, and C. M. Lieber, “Multiplexed electrical detection of cancer markers with nanowire sensor arrays”, Nat. Biotechnol., Vol. 23, No. 10, pp. 1294-1301, 2005.

[https://doi.org/10.1038/nbt1138]

-

A. Gao, N. Lu, Y. Wang, and T. Li, “Robust ultrasensitive tunneling-FET biosensor for point-of-care diagnostics”, Sci. Rep., Vol. 6, No. 1, pp. 1-9, 2016.

[https://doi.org/10.1038/srep22554]

-

A. M. Ionescu and H. Riel, “Tunnel field-effect transistors as energy-efficient electronic switches”, Nature, Vol. 479, No. 7373, pp. 329–337, 2011.

[https://doi.org/10.1038/nature10679]

-

A. C. Seabaugh and Q. Zhang, “Low-voltage tunnel transistors for beyond CMOS logic”, Proc. IEEE, Vol. 98, No. 12, pp. 2095–2110, 2010.

[https://doi.org/10.1109/JPROC.2010.2070470]

-

N. N. Reddy and D. K. Panda, “A Comprehensive Review on Tunnel Field-Effect Transistor (TFET) Based Biosensors: Recent Advances and Future Prospects on Device Structure and Sensitivity”, Silicon, Vol 13, pp. 3085-3100, 2021.

[https://doi.org/10.1007/s12633-020-00657-1]

-

S. Kanungo, S. Chattopadhyay, P. S. Gupta, K. Sinha, and H. Rahaman, “Study and Analysis of the Effects of SiGe Source and Pocket-Doped Channel on Sensing Performance of Dielectrically Modulated Tunnel FET-Based Biosensors”, IEEE Trans. Electron Devices, Vol. 63, No. 6, pp. 2589–2596, 2016.

[https://doi.org/10.1109/TED.2016.2556081]

-

D. Sarkar and K. Banerjee, “Fundamental Limitations of Conventional-FET Biosensors: Quantum-Mechanical-Tunneling to the Rescue”, in Proc. DRC, pp. 83-84, 2012.

[https://doi.org/10.1109/DRC.2012.6256950]

-

P. R. Nair and M. A. Alam, “Screening-Limited Response of NanoBiosensors”, Nano Lett., Vol. 8, No. 5, pp. 1281-1285, 2008.

[https://doi.org/10.1021/nl072593i]

-

M. Yokoyama, N. Taoka, R. Suzuki, O. Ichikawa, H. Yamada, N. Fukuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, “Sulfur cleaning for (100), (111)A, and (111)B InGaAs surfaces with In content of 0.53 and 0.70 and their Al2O3/InGaAs MOS interface properties”, in IPRM, pp. 167-170, 2012.

[https://doi.org/10.1109/ICIPRM.2012.6403348]

-

Y. Xuan, Y. Q. Wu and P. D. Ye, “High-Performance Inversion-Type Enhancement-Mode InGaAs MOSFET With Maximum Drain Current Exceeding 1 A/mm”, IEEE Electron Device Lett., Vol. 29, No. 4, pp 294-296, 2008.

[https://doi.org/10.1109/LED.2008.917817]

- J. Franco, A. Alian, B. Kaczer, D. Lin, T. Ivanov, A. Pourghaderi, K. Martens, Y. Mols, D. Zhou, N. Waldron, S. Sioncke, T. Kauerauf, N. Collaert, A. Thean, M. Heyns1, and G. Groeseneken1, “Suitability of high-k gate oxides for III-V devices: a PBTI study in In0.53Ga0.47As devices with Al2O3”, in IEEE Proc. IRPS, pp.6A.2.1-6A.2.6, 2014.

-

Y. Yuan, B. Yu, J. Ahn, P. C. McIntyre, P. M. Asbeck, M. J. W. Rodwell, and Y. Taur, “A Distributed Bulk-Oxide Trap Model for Al2O3 InGaAs MOS Devices”, IEEE Trans. Electron Devices, Vol. 59, No. 8, pp. 2100–2106, 2012.

[https://doi.org/10.1109/TED.2012.2197000]

-

G. F. Jiao, Z. X. Chen, H. Y. Yu , X. Y. Huang, D. M. Huang, N. Singh, G. Q. Lo, D. L. Kwong, M.-F. Li, “New Degradation Mechanisms and Reliability Performance in Tunneling Field Effect Transistors”, in IEDM Tech. Dig., pp. 1-4, 2009.

[https://doi.org/10.1109/IEDM.2009.5424234]

-

S. C. Kang , D. Lim, S. J. Kang, S. K. Lee, C. Choi , D. S. Lee, and B. H. Lee, “Hot-Carrier Degradation Estimation of a Silicon-on-Insulator Tunneling FET Using Ambipolar Characteristics”, IEEE Electron Device Lett., Vol. 40, No. 11, pp. 1716-1719, 2019.

[https://doi.org/10.1109/LED.2019.2942837]