Gate/Body-Tied 구조의 고감도 광검출기를 이용한 2500 fps 고속 바이너리 CMOS 이미지센서

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(https://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

In this study, we propose a 2500 frame per second (fps) high-speed binary complementary metal oxide semiconductor (CMOS) image sensor using a gate/body-tied (GBT) p-channel metal oxide semiconductor field effect transistor-type high-speed photodetector. The GBT photodetector generates a photocurrent that is several hundred times larger than that of a conventional N+/P-substrate photodetector. By implementing an additional binary operation for the GBT photodetector with such high-sensitivity characteristics, a high-speed operation of approximately 2500 fps was confirmed through the output image. The circuit for binary operation was designed with a comparator and 1-bit memory. Therefore, the proposed binary CMOS image sensor does not require an additional analog-to-digital converter (ADC). The proposed 2500 fps high-speed operation binary CMOS image sensor was fabricated and measured using standard CMOS process.

Keywords:

CMOS image sensor, Binary operation, Gate/Body-Tied photodetector, High-speed operation1. 서 론

최근 고집적화를 이용한 작은 크기의 소자 설계와 효율성이 큰 CMOS 이미지 센서는 인간의 눈을 대체할 만큼 그 성능이 발달되고 있으며, 이에 따라 최근 CMOS 이미지센서를 이용한 다양한 연구가 진행되고 있다. CMOS 이미지 센서는 주변회로를 집적화 할 수 있고 저 비용이 가능하여 휴대용 기기, digital single lens reflex (DSLR), 무인감시 카메라, 산업용 카메라 등 다양한 분야에 이용되고 있으며 관련 연구가 활발히 진행되고 있다[1-7]. CMOS 이미지 센서의 주요 연구 분야로는 전력소모, 감도, 동작속도, 동작영역 등이 있다. 그 중 이미지 센서의 감도는 CMOS 이미지 센서의 고해상도가 진행됨에 따라 화소크기가 작아지므로 감소된다. 이를 해결하기 위해 작은 화소 크기를 가지면서 고감도 특성을 가지는 광검출기의 사용이 필수 요소이다. 상용화된 일반 CMOS 이미지 센서 에서는 PN 접합 기반의 pinned photodiode (PPD)형 광검출기가 사용되고 있다[8]. CMOS 이미지 센서의 감도를 높이기 위해 PPD형 광검출기 보다 상대적으로 감도가 수십 배 큰 avalanche photodiode (APD)형 광검출기가 연구되고 있지만 CMOS 공정의 deep n-well 층의 사용으로 화소의 크기가 매우 크며 높은 전원 전압을 사용하기 때문에 고해상도/저전력 CMOS 이미지 센서에 적용하기에는 부적절 하다[9-10].

고감도 CMOS 이미지 센서 기술 개발뿐만 아니라 CMOS 이미지 센서의 저전력화와 동작 속도의 고속화는 모바일 기기 사용의 증가로 인해 관련 연구의 중요한 이슈가 되고 있다[11-12]. 모바일 기기의 배터리의 용량은 제한적이고 고해상도 이미지의 빠른 처리속도를 요구하기 때문에 이에 대한 많은 연구가 필요한 상황이다. 이미지 센서에서 동일한 전력 소모를 가질 때, 이미지의 해상도와 동작속도에 관계하는 1초당 프레임 수 (frame rate)는 상호 반비례 관계이며, 동일한 해상도에서 동작속도가 증가하면 전력소모는 그에 비례하여 증가하게 된다. CMOS 이미지 센서의 전력 소모는 칩을 구성하는 회로 중 증폭기 및 아날로그 디지털 변환기 등으로 구성된 리드아웃 회로에서 대부분의 전력이 소모되며 동작 속도는 아날로그 디지털 변환기의 변환 속도에 의해 제한된다고 할 수 있다.

본 연구에서는 고감도 특성을 가지는 GBT 구조의 광검출기를 이용하여 2500 fps 동작이 가능한 바이너리 이미지 센서를 제안한다. CMOS 바이너리 이미지 센서의 출력은 “0” 또는 “1”의 비트 값을 가지며, 추가적인 아날로그 디지털 변환기를 필요로 하지 않기 때문에 저전력 및 고속동작에 매우 유리하다. 제안한 이미지센서는 0.35 μm 표준 CMOS 공정을 사용하여 제작되었고 그 특성을 평가하였다. 제안한 이미지센서를 사용함으로써, GBT형 광검출기의 고감도 특성으로 인해 저 조도 현상에서도 물체 촬상이 가능하며, 바이너리 이미지 획득까지 추가적으로 가능하다. 이러한 바이너리 이미지 기술을 사용하여 바코드 인식, 움직임 감지 등 출력되는 이미지를 기준으로 흑색과 백색으로 판단하여야 하는 분야에 다양하게 사용될 것으로 기대된다.

2. 동작 원리

2.1 GBT PMOSFET타입 광검출기

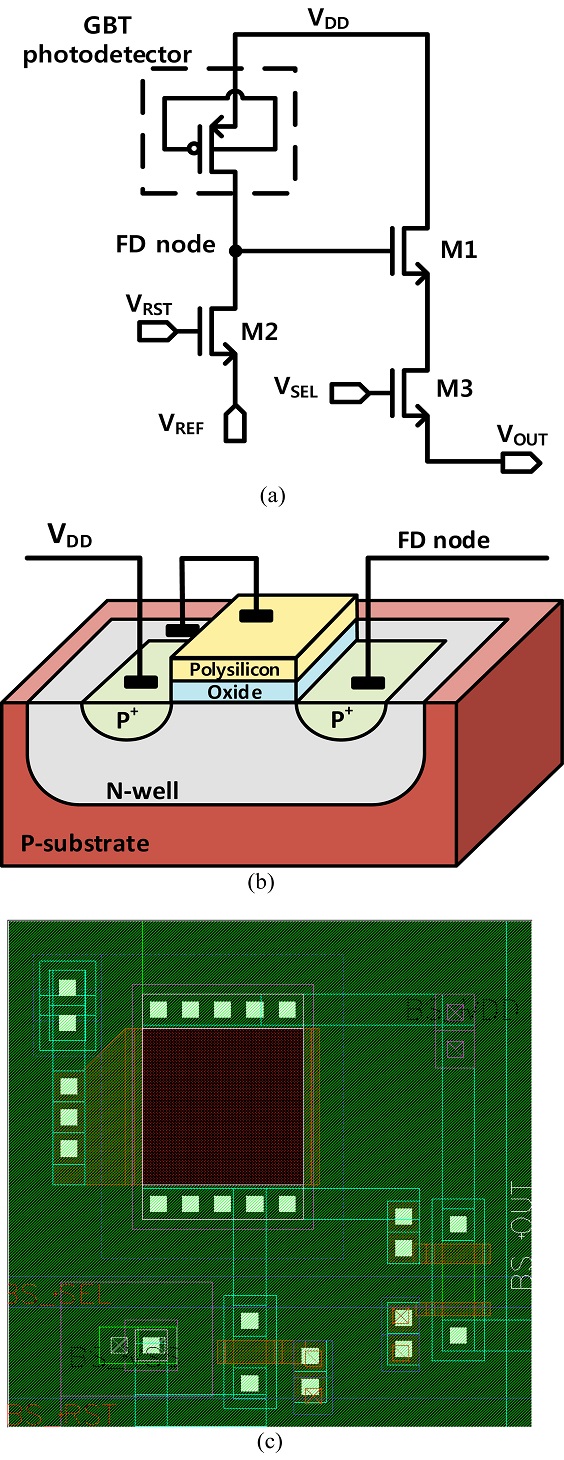

Fig. 1(a)는 GBT PMOSFET형 광검출기의 능동 화소 센서 구조의 회로도를 나타낸다. GBT 광검출기의 경우 GBT의 바디 영역에 존재하는 n-well 노드와 게이트 노드가 물리적으로 묶여서 설계된다. 또한 능동 화소 센서 구조로 설계하기 위해서 3개의 추가적인 NMOSFET이 집적된다. 추가적인 트랜지스터 중 M1 트랜지스터는 소스팔로워 역할을 함으로써 FD node의 전압을 증폭시키는 역할을 하며, M2 트랜지스터는 GBT형 광검출기의 리셋 동작을 수행하기 위해 집적되며, M3 트랜지스터는 원하는 타이밍에 신호 전압값을 샘플링하기 위한 셀렉트 트랜지스터로 동작을 한다.

Fig. 1(b)는 제작된 GBT의 수직 구조도를 나타낸다. GBT의 게이트를 통해 들어오는 입사광은 공핍 영역에서 전자-정공 쌍을 생성한다. 폴리실리콘 게이트와 P기판에 의해 유도된 전기장은 전자 정공 쌍을 분리한다. 정공은 GBT의 채널을 향해 드리프트 되고 GBT의 드레인 노드로 분리된다. 반대로 전자는 정공보다 전위 장벽이 높기 때문에 바디에 축적된다. 이러한 축적된 전자는 GBT의 게이트가 N-well에 연결되어 있기 때문에 GBT의 게이트에 음의 전압으로 작용하게 된다. 따라서 GBT의 게이트 전압이 감소하기 때문에 채널이 형성되고 형성된 채널로 인해 광 전류가 흐르게 된다. 또한 축적된 전자는 N-well에 음의 전압을 생성하게 되면서 positive feedback 효과가 GBT의 게이트에 발생한다. 따라서 GBT에 입사하는 빛에 의해 발생하는 광전류는 positive feedback 매커니즘에 의해 증폭되게 된다[13-14].

2.2 CMOS 바이너리 이미지 구현

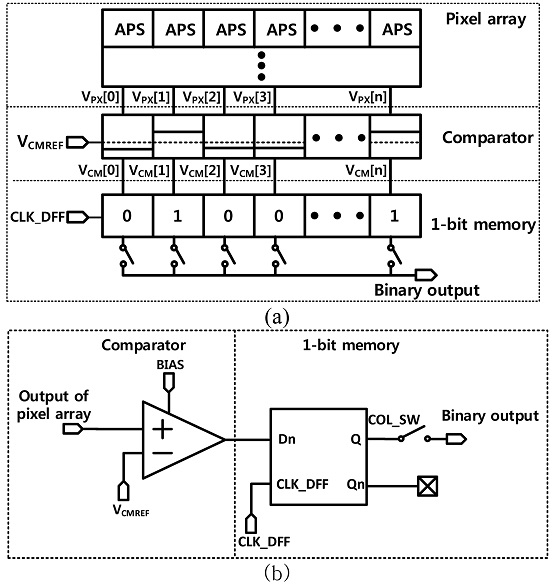

Fig. 2(a)는 GBT를 이용하여 제작한 CMOS 바이너리 이미지 센서의 바이너리 신호처리 시스템의 구조를 나타내며 Fig. 2(b)는 단위 칼럼 리드아웃 회로를 나타낸다. 제안한 CMOS 바이너리 이미지 센서는 GBT를 이용하여 제작된 픽셀 어레이, 바이너리 동작을 위한 비교기와 1비트 메모리로 구성되어 진다. 기존 CMOS 이미지 센서의 경우 멀티 비트 데이터를 얻기 위해 아날로그 디지털 변환기가 필요하지만 제안한 CMOS 바이너리 이미지 센서는 높은 프레임 레이트에서 1 비트 데이터에 대해이진 연산을 사용하여 영상을 출력하는 원리이다.

입사광 정보를 담고 있는 전압인 VPX는 칼럼 리드아웃 회로에 연결되며 이진 출력으로 변환된다. CMOS 바이너리 이미지 센서 신호 처리 회로는 일반적인 CMOS 이미지 센서 신호 처리 회로보다 간단하므로 상대적으로 고속동작이 가능하다.

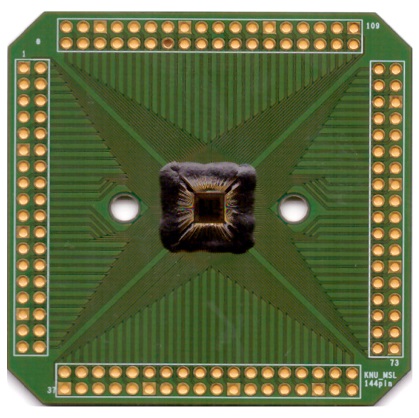

설계된 바이너리 이미지 센서는 CMOS 표준공정을 사용하여 제작되었으며, 전체적으로 픽셀 어레이, 칼럼 스캐너, 로우 스캐너, 바이너리 동작을 위한 리드아웃 회로로 구성되어 있다. Fig. 3은 제작된 CMOS 바이너리 이미지 센서가 부착된 PCB 기판을 보여준다.

3. 측정 결과 및 고찰

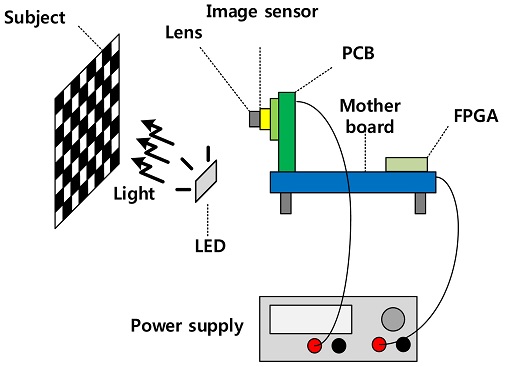

Fig. 4는 제작한 CMOS 바이너리 이미지 센서의 영상 획득을 위한 측정 시스템이다. 전원공급기는 마더보드와 PCB에 전원 전압을 공급한다. PCB와 마더보드는 이미지 센서를 구동시키기 위한 전압과 전류를 공급하고 마더보드에 부착된 FPGA는 이미지 센서를 구동시키기 위한 파형을 생성하여 이미지 센서에 입력된다. 피사체로 흑백의 사각형이 바둑판식으로 반복되는 패턴이 사용되었고, 피사체에 LED를 이용해 빛을 조사하였다. 이때, 피사체가 받는 빛의 세기는 1350 lux다. 피사체에 반사된 빛이 렌즈를 통해 이미지 센서에 들어오고 입사된 빛의 세기에 따라 픽셀 출력전압의 변화가 발생한다. 이때, 픽셀 출력전압은 리드아웃회로에서 처리되어 바이너리 이미지를 생성한다.

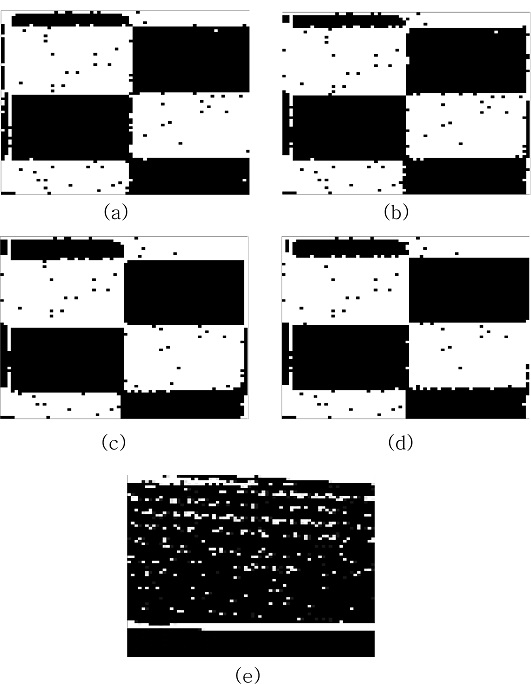

Fig. 5는 제작한 CMOS 바이너리 이미지센서를 사용하여 이미지 센서의 frame per second를 조절하여 얻은 바이너리 출력 이미지이다. 제작된 CMOS 바이너리 이미지센서의 고속동작을 확인 하기 위해서 1000, 1500, 2000, 2500, 3000 fps 로 동작을 시켜 동일 피사체를 대상으로 영상을 획득하였다. 출력된 바이너리 이미지는 비교기의 비교전압에 따라 “0”과 “1”을 판단하여 출력되는 영상이므로 고속동작을 하더라도 원 신호가 비교기의 비교 전압 이상 또는 이하로 훼손되지 않으면 출력되는 이미지의 왜곡이 없다. 측정 결과 2500 fps 이하의 경우에는 출력되는 영상의 왜곡이 발생하지 않았다. 그러나 3000 fps 까지 고속동작시에는 원신호에 왜곡발생 및 비교기의 “0”과 “1”을 판단하는 시간이 부족하여 바이너리 영상을 얻을 수 없음이 이미지를 통해 확인되었다. 따라서 기존의 비교기(2-stage comparator) 보다 더 동작속도가 빠른 비교기를 사용하면 3000 fps 이상으로 고속동작이 가능하리라 생각된다.

4. 결 론

본 논문에서는 고감도 특성을 가지는 GBT형 광검출기를 이용하여 고속동작이 가능한 CMOS 바이너리 이미지 센서를 설계 제작하고, 그 특성을 분석하였다. 제작된 CMOS 바이너리 이미지 센서는 최대 약 2500 fps 까지 바이너리 영상이 판독 가능함을 확인했으며, 비교기를 개선함으로써 3000 fps 이상의 고속동작이 가능하리라 생각된다. 바이너리 이미지 센서는 바코드 인식, 움직임 인식등 다양한 분야에 사용이 가능하며, 표준 CMOS 공정을 이용하여 제작가능 하므로 추가적인 공정이 필요하지 않다는 장점이 존재한다.

Acknowledgments

본 논문은 Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2018R1D1A3B0704995213) 와 Integrated Circuit Design Education Center (IDEC)의 지원에 의해 연구되었다.

REFERENCES

-

N. A. W. Dutton, L. Parmesan, A. J. Holmes, L. A. Grant and R. K. Henderson, “320 × 240 oversampled digital single photon counting image sensor”, 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, pp. 1-2, 2014.

[https://doi.org/10.1109/VLSIC.2014.6858428]

-

L. Yao, K. Y. Yung, R. Khan, V. P. Chodavarapu and F. V. Bright, “CMOS Imaging of Pin-Printed Xerogel-Based Luminescent Sensor Microarrays”, IEEE Sens. J., Vol. 10, No. 12, pp. 1824-1832, 2010.

[https://doi.org/10.1109/JSEN.2010.2047497]

-

T. Tokuda, H. Yamada, K. Sasagawa and J. Ohta, “Polarization-analyzing image sensor based on standard CMOS technology”, TRANSDUCERS 2009 - 2009 International Solid-State Sensors, Actuators and Microsystems Conference, Denver, CO, pp. 331-333, 2009.

[https://doi.org/10.1109/SENSOR.2009.5285497]

-

F. Raymundo, P. Martin-Gonthier, R. Molina, S. Rolando and P. Magnan, “Exploring the 3D integration technology for CMOS image sensors”, 2013 IEEE 11th International Workshop of Electronics, Control, Measurement, Signals and their application to Mechatronics, Toulouse, pp. 1-5, 2013.

[https://doi.org/10.1109/ECMSM.2013.6648935]

-

B.-S. Choi, S.-H. Kim, J. Lee, D. Seong, J.-K. Shin, J. Lim, S. Chang, J. Park, S.-J. Lee, and C.-M. Kyung, “In-Pixel Aperture CMOS Image Sensor for 2-D and 3-D Imaging”, IEEE Sens. J., Vol. 18, No. 22, pp. 9163-9168, 2018.

[https://doi.org/10.1109/JSEN.2018.2869383]

-

Y. Kitamura, H. Aikawa, K. Kakehi, T. Yousyou, K. Eda, T. Minami, S. Uya, Y. Takegawa, H. Yamashita, Y. Kohyama, and T. Asami, “Suppression of crosstalk by using backside deep trench isolation for 1.12 μm backside illuminated CMOS image sensor”, 2012 International Electron Devices Meeting, San Francisco, CA, pp. 24.2.1-24.2.4., 2012.

[https://doi.org/10.1109/IEDM.2012.6479093]

-

T. Hizawa, J. Matsuo, T. Ishida, H. Takao, H. Abe, K. Sawada, and M. Ishida, “32 × 32 pH Image Sensors for Real Time Observation of Biochemical Phenomena”, TRANSDUCERS 2007 - 2007 International Solid-State Sensors, Actuators and Microsystems Conference, Lyon, pp. 1311-1312, 2007.

[https://doi.org/10.1109/SENSOR.2007.4300379]

-

H. Alaibakhsh and M. A. Karami, “Analytical Modeling of Pinning Process in Pinned Photodiodes”, IEEE Transactions on Electron Devices, Vol. 65, No. 10, pp. 4362-4368, 2018.

[https://doi.org/10.1109/TED.2018.2862251]

-

B. Steindl, R. Enne, S. Schidl and H. Zimmermann, “Linear Mode Avalanche Photodiode with High Responsivity Integrated in High-Voltage CMOS”, IEEE Electron Device Letters, Vol. 35, No. 9, pp. 897-899, 2014.

[https://doi.org/10.1109/LED.2014.2336678]

-

K. Iiyama, H. Takamatsu and T. Maruyama, “Hole-Injection-Type and Electron-Injection-Type Silicon Avalanche Photodiodes Fabricated by Standard 0.18- μm CMOS Process”, IEEE Photonics Technology Letters, Vol. 22, No. 12, pp. 932-934, 2010.

[https://doi.org/10.1109/LPT.2010.2047389]

- A. O. Ercan, Feng Xiao, Xinqiao Liu, SukHwan Lim, A. El Gamal and B. Wandell, “Experimental high speed CMOS image sensor system and applications”, SENSORS, 2002 IEEE, Orlando, FL, USA, pp. 15-20, 2002.

-

M. M. El-Desouki, O. Marinov, M. J. Deen and Q. Fang, “CMOS Active-Pixel Sensor with In-Situ Memory for Ultrahigh-Speed Imaging”, IEEE Sens. J., Vol. 11, No. 6, pp. 1375-1379, 2011.

[https://doi.org/10.1109/JSEN.2010.2089447]

-

H. H. Lee, S. H. Jo, M. Bae, B. S. Choi, H. Kim, H. K. Lyu, and J. K. Shin, “Highly sensitive gate/body-tied metaloxide-semiconductor field-effect transistor-type photodetector with wavelength-selective metal grid structure using standard complementary metal-oxide-semiconductor technology”, Sens. Mater., Vol. 27, No. 1, p. 135–142, 2015.

[https://doi.org/10.18494/SAM.2015.1079]

-

M. Lee, S. H. Jo, M. Bae, B. S. Choi, P. Choi, and J. K. Shin, “Modeling of Gate/Body-Tied PMOSFET Photodetector with Built-in Transfer Gate”, J. Sens. Sci. Technol., Vol. 23. No. 4, pp. 284-289, 2014.

[https://doi.org/10.5369/JSST.2014.23.4.284]