공통-모드 간섭 (CMI)에 강인한 2-전극 기반 심전도 계측 회로

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(https://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

This study introduces an efficient readout circuit designed for two-electrode electrocardiogram (ECG) recording, characterized by its low-noise and low-power consumption attributes. Unlike its three-electrode counterpart, the two-electrode ECG is susceptible to common-mode interference (CMI), causing signal distortion. To counter this, the proposed circuit integrates a common-mode charge pump (CMCP) with a window comparator, allowing for a CMI tolerance of up to 20 VPP. The CMCP design prevents the activation of electrostatic discharge (ESD) diodes and becomes operational only when CMI surpasses the predetermined range set by the window comparator. This ensures power efficiency and minimizes intermodulation distortion (IMD) arising from switching noise. To maintain ECG signal accuracy, the circuit employs a chopper-stabilized instrumentation amplifier (IA) for low-noise attributes, and to achieve high input impedance, it incorporates a floating high-pass filter (HPF) and a current-feedback instrumentation amplifier (CFIA). This comprehensive design integrates various components, including a QRS peak detector and serial peripheral interface (SPI), into a single 0.18-μm CMOS chip occupying 0.54 mm2. Experimental evaluations showed a 0.59 μVRMS noise level within a 1–100 Hz bandwidth and a power draw of 23.83 μW at 1.8 V.

Keywords:

Low-noise, Low-power, Common mode charge pump (CMCP), Common mode interference (CMI), Window comparator, Current feedback instrumentation amplifier (CFIA)1. 서 론

심전도 신호의 측정은 부정맥, 심방 세동, 허혈성 심장질환, 심방/심실 비대, 전해질 이상 등 여러 가지 심혈관계 질환을 진단하는 데 중요한 지표가 된다 [1]. 또한, 최근 현대인들의 건강에 대한 관심으로 인해 심전도 측정 센서 시장도 활발히 증대되고 있다. 심전도 신호 센서 시장이 증대됨에 따라, 의료시설뿐만 아니라 개인이 직접 심전도를 측정할 수 있는 휴대용 심전도 측정기의 관심도도 높아지고 있다 [2]. 따라서, 본 논문에서는 기존의 3-전극 방식과 달리 휴대성과 장시간 모니터링이 필요한 사용자에게 편리함을 주는 2-전극 방식의 심전도 측정 방식을 도입하였다. 본 논문에서는 2-전극 방식을 사용할 때 제거가 필요한 공통-모드 간섭 성분을 감소시키는 common-mode charge pump (CMCP)를 도입한 저잡음 및 저전력 특성을 가지는 심전도 측정 회로를 제안한다.

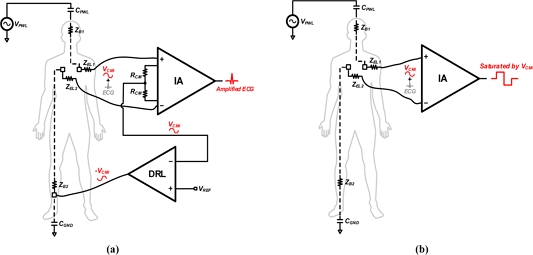

기존의 심전도 측정 방식은 3-전극 방식 또는 2-전극 방식이 있다. 주로 사용되는 3-전극 방식의 기본 구조는 Fig. 1(a)와 같다. 기존의 3-전극은 2개의 심전도 측정용 전극과 공통-모드 간섭 (common-mode interference, CMI)을 감소시키기 위한 1개의 전극으로 구성된다. 공통-모드 간섭 감소는 1개의 전극을 인체의 오른쪽 다리를 통해 접지 또는 Driven right leg (DRL) 회로에 연결하여, Fig. 1(a)와 같이 피드백을 통해 생체 임피던스 (ZB1, ZB2)에 의해 생성되는 공통-모드 간섭 (CMI)를 감소시켜준다 [3,4]. 따라서, 3-전극 방식을 이용하면 공통-모드 간섭에 상관없이 고해상도의 심전도 신호를 획득할 수 있다. 하지만 3번째 전극을 오른쪽 다리에 연결해야 하므로 장시간 측정에 있어 사용자에게 불편함을 주게 된다. 따라서, 이러한 3번째 전극을 제거하여 사용자에게 편안함과 이동성을 주기 위해 최근에는 2-전극 방식의 심전도 측정 방식이 주목받고 있다.

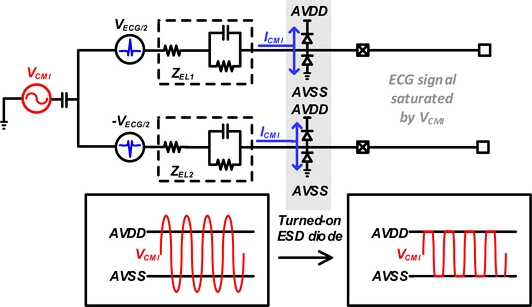

기존 3-전극 방식에서 세 번째 전극을 제거한 2-전극 방식은 Fig. 1(b)와 같다. 2-전극 방식은 사용자에게 편리함을 주는 대신 치명적인 단점이 존재하게 된다. 기존의 공통-모드 간섭을 막아주는 3번째 전극의 부재로 인해 2개의 전극을 통한 심전도 (ECG) 신호가 포화하게 된다. Fig. 2는 공통-모드 간섭에 의해 electro-static discharge (ESD) 다이오드의 동작 따라 심전도 신호가 측정되지 않는 현상을 나타냈다. ESD 다이오드는 회로의 전원 전압보다 높은 전압 범위의 공통-모드 간섭이 발생할 때 활성화된다. ESD 다이오드의 동작으로 인해 전극에서 발생하는 전류 (ICMI)는 전원과 접지 쪽으로 흐르게 된다. 따라서, 전원 전압보다 큰 CMI에 의해 심전도 신호의 포화가 발생하여 계측 증폭기 (IA)를 통한 측정이 불가하게 된다 [6,7].

본 논문에서는 2-전극 방식의 위와 같은 문제점을 해결하기 위해 2개의 전극과 계측 증폭기 사이에 common-mode charge pump (CMCP) 구조를 추가하여, 공통-모드 간섭을 감소시켰다. CMCP를 통해 생체 임피던스에서 발생하는 공통-모드 간섭을 감소시키고, 계측 증폭기에 일정한 공통-모드 동작 범위 (common-mode range)를 유지시켜 정확한 심전도 신호를 전달할 수 있다.

따라서, 본 논문에서는 휴대 및 장시간 모니터링에 용이한 2-전극 기반의 심전도 측정 회로를 제안한다. 제안하는 회로는 CMCP, 심전도 증폭 회로로 구성되어 있다.

2. 회로 설계

2.1 전체 회로 설계

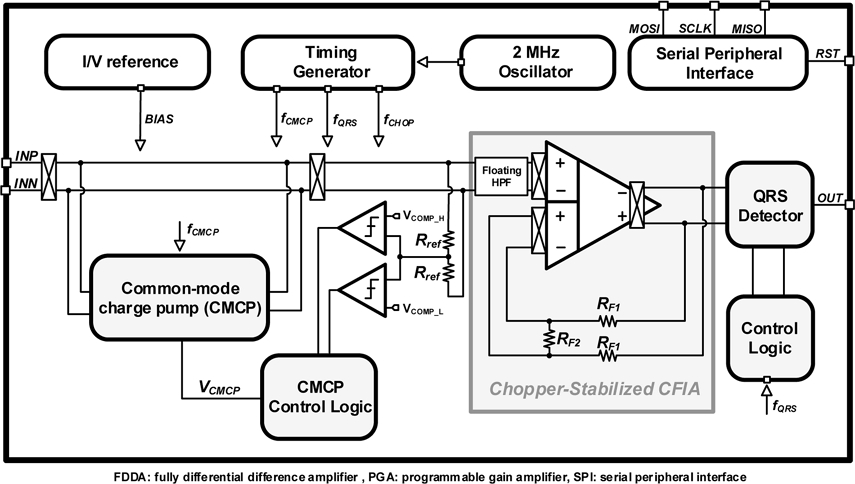

Fig. 3는 본 논문에서 제안하는 2-전극 방식의 심전도 측정 회로도이다. 제안하는 회로에 필요한 성능은 다음과 같다. 먼저, 공통-모드 간섭 (CMI) 성분을 효과적으로 감소시켜주는 방식을 CMCP를 통해 감소시켰다. 또한 심전도 증폭 회로에 floating high-pass filter (HPF) 및 쵸퍼 안정화 기법을 적용하여 1-2 mV의 작은 심전도 신호를 높은 정확도를 가진 증폭이 가능하다.

제안하는 회로는 CMCP, 심전도 신호 측정 회로, 서브 블록으로 크게 세 가지로 구성했다. CMCP는 switched-커패시터로 구성된 charge pump, control logic, window comparator, buffer로 구성되어 있다. 제안하는 논문에서는 window comparator 구조를 이용하여 공통-모드 동작 범위의 영역 내에서 상한선(VCOMP_H)과 하한선(VCOMP_L)을 정해주었다. 또한, 지정한 범위 내에서는 CMCP를 동작 시키지 않아 추가적인 전력소모를 줄 일 수 있었다. CMCP 루프에 쵸퍼 안정화 기법을 적용하여 CMCP 동작에서 발생하는 DC 오프셋 및 저주파 대역의 잡음 성분을 감소시켰다.

심전도 신호 측정 회로는 floating high-pass filter (HPF), CFIA, QRS peak detector로 구성되어 있다. Floating HPF의 경우, 전극에서 발생하는 임피던스 매칭의 오차를 줄여 주고, DC 대역의 신호 및 잡음을 감쇠 시켜 일정한 공통-모드 동작 범위를 확보하는 역할을 한다. CFIA는 기존의 capacitive coupled instrumentation amplifier (CCIA) 구조에 비해 입력단에 추가적인 커패시터가 존재하지 않아 높은 입력 임피던스를 가진다는 특징이 있고, 3-operational amplifier instrumentation amplifier (3-opamp IA) 구조에 비해 전력 소모 및 면적 측면에서 장점이 있다. 따라서, 본 논문에서는 장시간 효과적으로 정확한 ECG 신호를 모니터링하기 위해 위에서 제시한 다른 구조들에 비해 상대적으로 저전력 및 높은 선형성을 가지는 구조인 CFIA 구조를 채택하였다. 또한, CFIA에 쵸퍼 안정화 기법을 적용하여 DC 오프셋 및 저주파 대역의 잡음 성분을 감소시켰다. QRS peak detector는 심전도의 P-Q-R-S-T 신호 중 QRS 부분의 신호를 검출하여, 심박수 측정 및 분석에 사용된다. 비교기를 통해 기준 전압과 증폭된 심전도 신호를 비교하여, R 신호를 만나면 control logic을 통해 QRS peak를 검출할 수 있다.

제안하는 회로는 추가적으로 많은 수의 레지스터들을 세팅하기 위해 외부와 통신이 가능한 serial peripheral interface (SPI)를 내장하였고, 증폭기의 기준 전압 및 회로에서 사용되는 일정한 기준 전압을 주기 위한 current/voltage reference를 추가하였으며, 쵸퍼 동작과 CMCP 동작을 위해 oscillator를 통해 일정한 클럭 주파수를 만들어 주는 timing generator로 구성되어 있다.

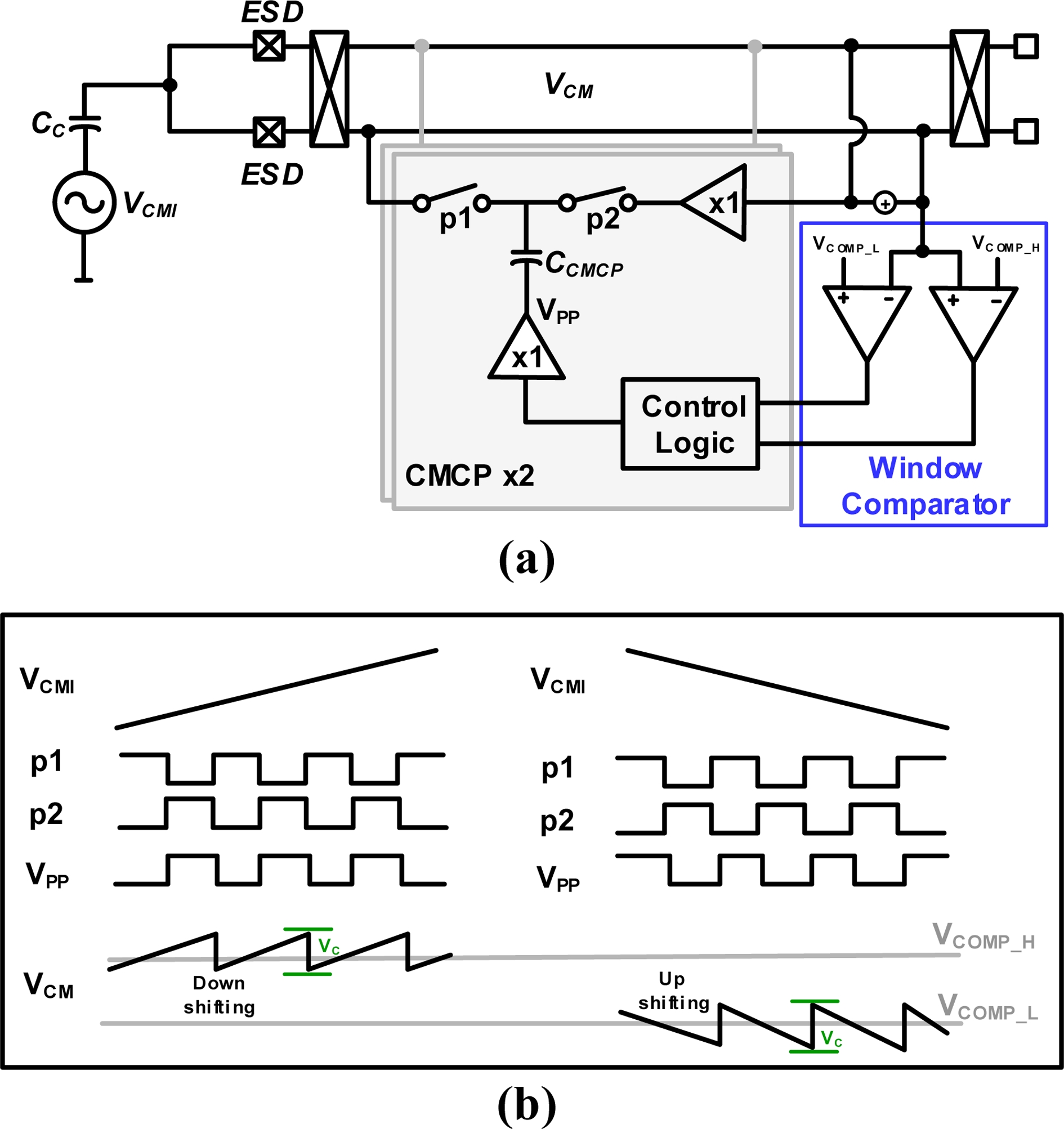

2.2 Common-Mode Charge Pump

Fig. 4는 제안하는 CMCP의 구조를 나타낸다. CMCP의 구조는 switched-커패시터, window comparator, 컨트롤 로직, 버퍼로 구성된다. 기존의 제안되었던 CMCP는 single comparator가 사용된다 [6,7]. 본 논문에서는 기존의 comparator 구조와 다른 window comparator를 적용하였다. Window comparator는 동작 범위의 상한선(VCOMP_H)과 하한선(VCOMP_L)의 window 범위가 생성된다. 기존의 CMCP 구조에서는 일정한 공통-모드 범위에서도 계속 CMCP가 동작하여 전력 소모 및 switching으로 인한 switching noise 및 intermodulation distortion (IMD)이 심전도 신호의 왜곡을 발생시키게 된다. 본 논문에서는 window 범위 내에서는 CMCP 동작을 멈추어 전력 소모를 감소시켰고, switching 동작을 멈춰 IMD 발생을 감소시켜 신호의 왜곡을 줄일 수 있게 되었다. 제안하는 회로는 전원 전압 1.8 V에서 동작하며, window comparator의 동작 상한선은 1.1 V, 하한선은 0.7 V로 설정하였다.

공통-모드 간섭이 기준 전압의 상한선 (VCOMP_H)보다 증가할 때, comparator의 비교 동작에 의해 VPP가 high (1.8V) 상태가 된다. 그 후, p2 페이즈에서 커패시터가 일정한 전압을 충전한 상태로 유지가 되고, p1 페이즈에서 입력 쪽으로 피드백 루프를 통해 전압을 통과시켜 공통-모드 간섭 전압을 낮추어 comparator 상한 기준 전압의 상한선 (VCOMP_H=1.1V)로 전압을 유지시키게 된다. 반대로 공통-모드 간섭 전압이 기준 전압의 하한선 (VCOMP_L) 보다 감소할 때, comparator의 기준 전압과 공통-모드 간섭 전압에 비교 동작에 의해 VPP가 low (0V) 상태가 된다. 그 후, p2 페이즈에서 커패시터에 일정한 전압을 유지시킨 후, p1 페이즈에서 피드백을 통해 공통-모드 간섭 전압을 기준 전압의 하한선(VCOMP_L = 0.7 V)로 유지시킨다.

CMCP에서 구성되는 커패시터의 값은 2 pF, 10 pF를 programmable 하게 선택할 수 있도록 구성하였다. 공통-모드 간섭이 입력되는 coupling 커패시터를 220 pF로 가정하였을 때, CMCP의 동작에 의해 조정되는 전압의 양 (VC)는 다음과 같이 나타낼 수 있다.

| (1) |

제작한 회로의 전원 전압 (VDD)는 1.8 V이다. 위의 식을 바탕으로 계산하였을 때, CMCP 동작을 통한 전압의 변화량 (VC)은 CMCP 커패시터 (CCMCP)가 2 pF 일 때 32 mV, 10 pF 일 때 150 mV 수준이다.

제안하는 CMCP의 감소 가능한 최대 공통-모드 간섭의 전압 범위 (VTolerance)는 다음과 같이 나타낼 수 있다. 먼저 CMCP 동작 주파수 (fCMCP)와 CMCP 동작 변화량 (VC)에 따른 공통-모드 간섭 전압의 최대 제어 범위는 다음과 같이 나타낼 수 있다.

| (2) |

위 식에서 VCMI가 sinusoidal 파형일 때 진폭을 ACMI라고 설정하고, 식(1)을 대입하여 비교하면 다음과 같은 식이 성립된다.

| (3) |

CC는 입력 공통-모드 간섭에 대한 coupling 커패시터이고, 최대 제어 가능한 공통-모드 간섭에 대한 최대 전압 범위는 진폭(ACMI)의 2배인 peak-to-peak 전압 (VTolerance)으로 나타낼 수 있다.

| (4) |

공통-모드 간섭 전압은 전원 선을 통해 인체 임피던스로 전달되기 때문에 coupling 커패시터 (CC = 220 pF), 공통-모드 간섭 주파수 (fCMI = 60 Hz)로 설정하였다. 본 논문에서 적용한 CMCP의 주파수 (fCMCP = 125 kHz)와 커패시터 (CCMCP = 2 pF)를 식 (4)에 대입해 보면 제안하는 CMCP에서 제어가 가능한 최대 공통-모드 간섭 전압 범위는 21.3 V 임을 알 수 있다.

또한, 추가적인 잡음 성분을 감소시키기 위해, CMCP 루프에 쵸퍼 안정화 기법을 적용하여, 저잡음 대역의 1/f corner 잡음 성분을 감소시켰다. 쵸퍼 안정화 기법 적용 전 CMCP 루프의 input referred noise 시뮬레이션 결과, 1 Hz에서 1.3 μV/√Hz로 나타났다. 쵸퍼 안정화 기법을 적용하였을 때의 시뮬레이션 결과는 1 Hz 대역폭에서 66.47 nV/√Hz를 만족하여 약 20배가량 저주파 대역의 입력 잡음 성분이 감소함을 확인하였다.

CMCP에 사용되는 buffer는 PMOS 입력단을 이용한 folded-cascode 구조를 적용하였다. Folded-caocde 구조는 DC gain 과 unit gain bandwidth 향상에 장점을 갖는다. 입력단의 전류 소스에서 흐르는 전류는 589 nA, cascade 단에서 흐르는 전류는 각각 220 nA 수준이다. 따라서, buffer의 총 사용 전류 소모량은 1.029 μA이다.

CMCP에 사용된 comparator의 입력은 기준 전압과 공통-모드 간섭 전압이며, 설계한 comparator는 2단의 preamplifier와 latch로 구성된다. Cascode 형태로 구성된 2개의 preamplifier는 입력신호를 비교 가능한 충분한 전압으로 증폭한다. 이 후, NMOS와 PMOS로 구성된 CMOS latch는 이를 다시 한번 증폭한다. 즉, positive 입력단이 negative 입력단 보다 조금이라도 클 경우 출력전압은 high (1.8 V)가 된다.

Comparator 내 latch는 clock을 사용하며, 이를 통해 회로를 reset할 수 있다. Latch의 clock 신호가 high일 경우 current를 공급하는 PMOS가 off 되어 동작하지 않으며, clock 신호가 low일 경우에만 동작하게 된다. 결과적으로 설계한 comparator는 falling edge에서 동작하게 되며, 동작하지 않을 때는 전류를 소비하지 않아 저전력 특성을 가지게 된다.

2.3 심전도 신호 측정 회로

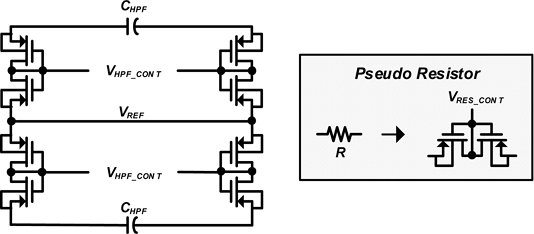

Fig. 5는 제안하는 회로에 적용된 floating HPF 회로이다. Floating HPF는 DC 오프셋 성분을 감소시키기 위해 적용되었다. 제안하는 Floating HPF는 4개의 pseudo 저항과 2개의 커패시터로 이루어져 있다. DC 오프셋을 제거하기 위해선 신호 수집 대역폭보다 낮은 차단 주파수 대역이 필요하기 때문에 수동 소자로 저항을 구성할 경우 매우 넓은 면적을 차지하게 된다. 따라서 본문에서는 회로의 면적을 줄이기 위해 pseudo 저항을 적용하여, 2개의 PMOS와 컨트롤 전압 (VRES_CONT)을 통해 구성하였다 [7]. Pseudo 저항은 컨트롤 전압 (VRES_CONT)를 통해 조절된다.

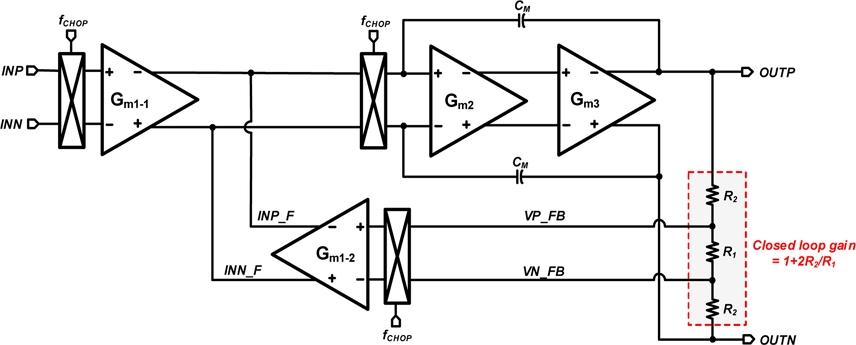

Fig. 6는 제안하는 CFIA 회로의 블록 다이어그램이다. IA로 자주 사용되는 capacitive coupled instrumentation amplifier (CCIA) 구조의 경우 입력을 커패시터로 받아 입력 임피던스 특성이 좋지 않은 단점이 있다 [8,9]. 반면, 제안하는 회로에 적용한 CFIA는 transistor의 gate 단으로 직접 입력을 받아, 입력 임피던스의 값이 크다는 장점이 있다. 또한, 3개의 OPAMP가 사용되는 3-operational amplifier instrumentation amplifier (3-OPAMP IA) 구조에 비해 면적 측면에서 장점을 가질 수 있다 [10]. CFIA는 입력 transconductance (Gm1-1, Gm1-2)와 Miller integrator (Gm2, Gm3)으로 구성되어 있다. Miller integrator 단은 주파수 응답을 향상 시키기 위해, unit gain bandwidth 및 phase margin 특성에 강점을 주는 nested-Miller compensation을 적용하였다. CFIA의 전달함수는 식(5)와 같이 나타낼 수 있다.

| (5) |

회로에서 사용된 R2와 R1은 CFIA의 피드백 저항이다. 이상적으로 Gm1-1과 Gm1-2의 비율의 매칭이 잘 되어있어, 거의 같은 수치일 때, 식(6)과 같이 전달함수 식을 간략화 하여 나타낼 수 있다.

| (6) |

따라서, CFIA의 closed loop gain은 식 (6)으로 나타낼 수 있으며, 제안하는 회로는 피드백 저항을 각각 R2 = 10 MΩ, R1 = 100 kΩ로 설정해 약 201배 (46 dB) 수준의 closed loop gain으로 입력 받은 심전도 신호를 증폭하게 된다 [11,12].

제안하는 CFIA는 저주파 대역의 잡음 성분을 줄이기 위해 쵸퍼 안정화 기법이 적용되었다. 쵸퍼 안정화 기법 적용 전의 잡음 수준은 시뮬레이션 결과 1 Hz에서 1.3 μV/√Hz을 가지고, 1 kHz에서 72 nV/√Hz을 가지게 된다. 쵸퍼 안정화 기법을 적용 후에는 1 Hz에서 123 nV/√Hz을 가지고, 1 kHz에서 59 nV/√Hz을 가지게 되어 쵸퍼 안정화 기법을 적용하여 1 Hz 대역폭에서 약 10배 정도의 잡음 수준 감소를 달성하였다.

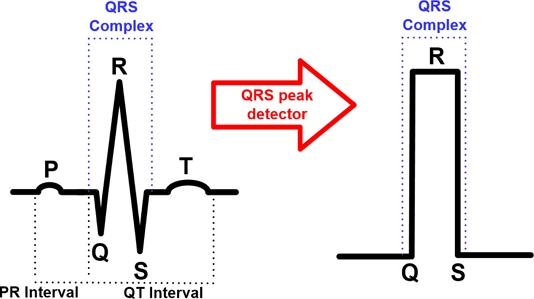

심전도 신호에는 P-Q-R-S-T complex가 존재한다. 제안하는 QRS peak detector 회로는 CFIA를 통해 증폭된 심전도 신호 중 Fig. 7에 나타낸 것과 같이, P-Q-R-S-T complex 중 QRS complex를 추출하는 회로이다 [14].

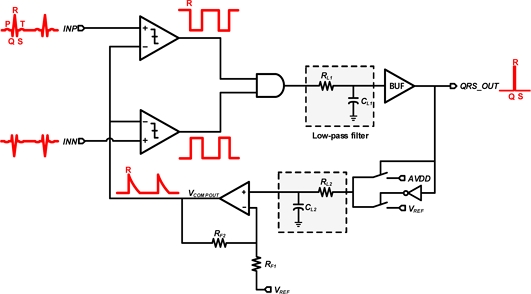

Fig. 8은 제안하는 QRS peak detector 회로이다. 제작한 회로는 comparator, AND gate, low-pass filter (LPF), amplifier로 구성된다. INP를 기준으로 증폭된 심전도 신호가 입력될 때, Rterm의 전압이 comparator의 기준 전압 (VREF)보다 높아지면 VCOMPOUT를 low (0 V)로 낮아지게 된다. VCOMPOUT이 낮아지게 되면, AND gate 및 로직을 통해 기준 전압 (VREF)의 전압이 high (1.8 V)로 올라가게 된다. 심전도 신호가 기준전압보다 낮아질 때, 올라갔던 기준 전압이 로직을 통해 high 1.8 V에서 서서히 VREF로 감소하게 된다. 반대의 경우에도 동일한 과정을 거칠 때, 두개의 VCOMPOUT을 AND gate로 거치게 되면, QRS complex 파형을 검출할 수 있게 된다.

3. 제작 및 성능 평과 결과

3.1 각 제작 결과

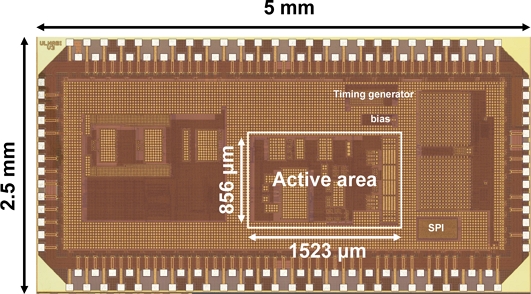

Fig. 9은 제작된 공통-모드 간섭을 줄인 2-전극 기반 심전도 측정 회로를 나타내었다. 본 논문에서 제안한 심전도 측정 회로는 standard 0.18 μm CMOS 공정을 사용하여 제작되었다. 전체 칩의 size는 5 mm× 2.5 mm로 제작되었으며, 제작된 칩의 활성 면적 (active area)는 0.856 mm × 1.523 mm이며, 칩 내에는 심전도 측정용 CMCP, CFIA, QRS detector, 2 MHz oscillator, timing generator, I/V reference, SPI 등이 모두 하나의 칩에 집적화 되어있다.

3.2 성능 평과 결과

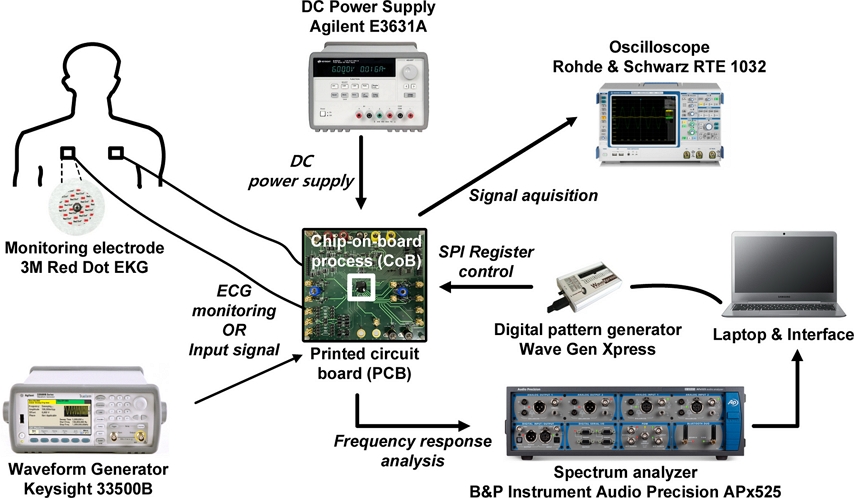

Fig. 10 은 설계 및 제작한 심전도 측정 회로의 측정 모식도를 나타내었다. 제작된 칩은 chip-on-board (CoB) process를 이용해 제작한 printed circuit board (PCB)에 증착하였다. PCB에는 측정을 위해 실제 전극 임피던스를 기반으로 모델링 한 임피던스를 추가하여 설계하였다 [15]. 제작된 회로의 성능 분석을 위해 waveform function generator를 이용하여 임의의 공통-모드 간섭 전압을 인가하였고, oscilloscope와 spectrum analyzer를 통해 분석을 진행하였다. Power supply를 통해 1.8 V의 전원 전압을 인가하였다. 제작된 회로의 레지스터는 SPI를 통해 노트북에서 설정한 레지스터 인터페이스를 이용해서 조절할 수 있다. 제작한 회로의 실제 심전도 측정을 위해 3M 사의 ECG electrode를 사용하여 회로와 연결하여 oscilloscope를 통해 측정을 진행하였다.

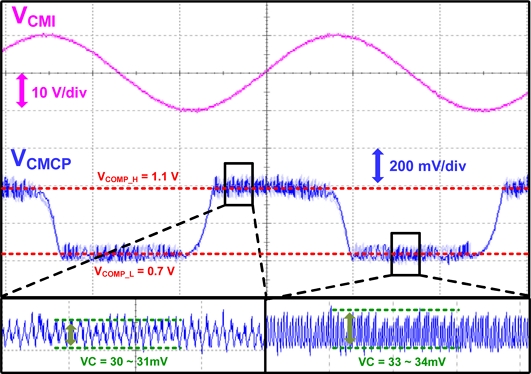

Fig. 11은 제작된 심전도 측정 회로의 CMCP 측정 결과를 나타낸다. 제안하는 회로는 위의 본문 식(2)를 통해 계산하였을 때, 최대 진폭 21.3 V의 sinusoidal 공통-간섭 모드 전압 범위까지 제어가 가능하다는 계산 값을 도출하게 되었다. 일반적으로 존재하는 생체 임피던스를 통한 coupling 커패시터 (Cc) 값을 220 pF로 모델링 하여 PCB를 구성하고 function generator를 통한 진폭 20 V의 사인파 신호를 입력하여 실험을 진행하였다. 측정 결과, 최대 20 V의 진폭을 가진 공통-모드 간섭 전압에 대해 전압이 상승할 경우 기준 전압 상한선 (VCOMP_H = 1,1 V)로 잘 유지됨을 확인하였고, 전압이 하강할 경우 기준 전압 하한선 (VCOMP_L = 0.7 V)로 유지됨을 확인하였다. 따라서, 제안하는 회로를 통해 최대 20 VPP의 공통-모드 간섭 전압을 제어할 수 있음을 확인하였다.

식(1)을 통해 CMCP 동작에 따른 제어 전압의 변화량 (VC)은 CMCP 커패시터 (CCMCP) 2 pF로 설정하였을 때, 32 mV 임을 도출하였다. 실제 측정 결과, 상승 전압 제어 시에 제어 전압의 변화량 (VC)은 30 ~ 31 mV, 하강 전압 제어 시에 전압의 변화량 (VC)은 33 ~ 34 mV로 측정 시 외부 요인을 감안하였을 때, 계산 값과 유사한 제어 전압의 변화량을 가짐을 확인하였다.

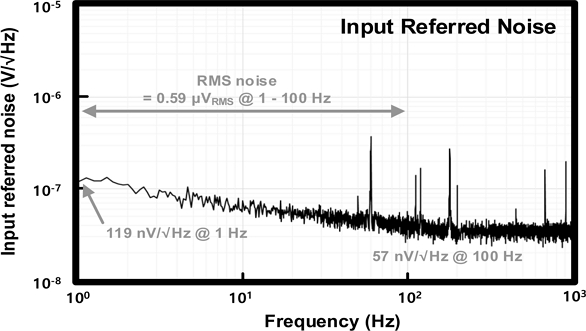

Fig. 12는 제작된 심전도 측정 회로의 input-referred noise 측정 결과를 나타낸다. 제안하는 회로는 쵸퍼 안정화 기법을 통해 저주파 대역의 저잡음 특성을 달성하였다. 실제 측정한 input-referred noise는 1 Hz 대역폭에서 119 nV/√Hz 값을 가지며, 100 Hz 대역폭에서는 57 nV/√Hz의 값을 가진다. 잡음 성분의 RMS 잡음을 계산하는 식은 다음과 같다.

| (7) |

ω1, ω2는 원하는 주파수 대역의 시작 주파수와 정지 주파수를 의미하고, Vnoise는 각각의 주파수에 해당되는 spot noise 성분을 의미한다. 심전도 신호의 유효 대역폭은 1 ~ 100 Hz이다. 따라서 식(7)에 대입하였을 때, 1 ~ 100 Hz 대역폭에서 실측 결과를 통한 RMS 잡음 수치는 0.59 μVRMS를 가짐을 확인하였다.

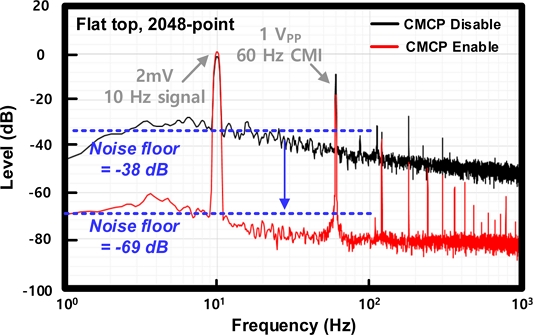

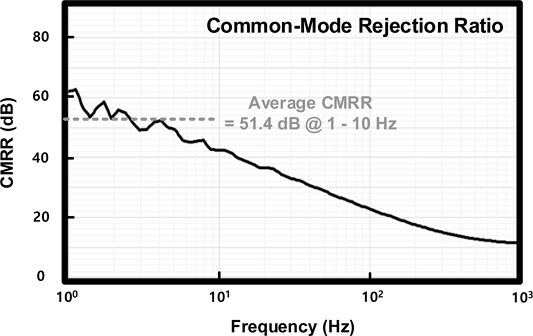

Fig. 13은 제작된 심전도 측정 회로의 fast Fourier transform (FFT) 측정 결과를 나타낸다. 측정은 spectrum analyzer를 통해 진행하였으며, window 형식은 flat-top, point 수는 2048개로 설정하였다. 입력에 2 mV의 10 Hz sinusoidal 파형을 인가하고 1 V의 60 Hz sinusoidal 공통-모드 간섭 전압을 PCB를 통해 인가하였을 때, CMCP가 동작하지 않을 때의 잡음 레벨은 -38 dB를 획득하였으며, CMCP가 동작하였을 경우 -69 dB의 잡음 레벨을 획득하였다. 측정 결과, CMCP가 동작 했을 때, 잡음 레벨 감소량은 31 dB로 CMCP가 동작하지 않았을 경우보다 왜곡이 감소된 신호를 획득할 수 있음을 확인하였다. Fig. 14은 제작된 심전도 측정회로의 common-mode rejection ratio (CMRR) 측정 결과를 나타낸다. 측정된 CMRR은 1 ~ 10 Hz 대역폭에서 51.4 dB를 획득하였다.

Table 1은 제안하는 심전도 측정 회로와 기존 연구들의 성능 비교 결과를 나타낸다. 제안하는 회로는 전력 소모 및 잡음 특성, 최대 제어 가능한 공통-모드 간섭 전압에서 장점을 가짐을 확인하였다. 표에서 제시한 잡음 효율 계수 (noise efficiency factor, NEF)는 다음 식과 같다.

| (8) |

4. 결론 및 향후 연구

본 논문은 최대 공통-모드 간섭 (CMI)에 강인한 저전력 및 저잡음 특성을 가지는 2-전극 측정 방식 기반 심전도 계측 회로를 제안한다. 본 논문에서는 새로운 구조의 CMCP 구조를 제안하여 2-전극 기반 측정 방식에서 발생하는 문제점인 공통-모드 간섭 전압을 효과적으로 제어한다.

제안하는 회로는 CMCP 단, 심전도 신호 증폭 단 및 기타 서브 블록으로 구성된다. CMCP 단은 switched-커패시터 구조, window comparator, 컨트롤 로직으로 구성된다. Window comparator 구조를 사용하여 동작 가능한 공통-모드 전압 동작 범위 내에서는 comparator의 동작을 멈추어, 추가적인 전력 소모를 감소시키고 switching noise에 인해 발생되는 IMD를 감소시키는 데 도움을 준다. 심전도 신호 증폭 단은 floating HPF, CFIA, QRS peak detector로 구성된다. Floating HPF를 통해 큰 DC 오프셋 성분을 감소시킬 수 있고, 높은 입력 임피던스를 가진 CFIA를 통해 오차가 작은 신호를 입력 단으로 전달받아 심전도 신호를 증폭한다. QRS peak detector를 통해 증폭된 심전도 신호의 QRS peak를 검출할 수 있다.

제안하는 회로는 0.18 μm CMOS 공정으로 제작되었으며, 활성 면적은 0.54mm2이다. 본 논문에서는 쵸퍼 안정화 기법을 적용하여, 심전도 신호 검출 대역폭인 1-100 Hz 대역폭에서 0.59 μVRMS의 저잡음 특성을 확보하였다. 또한, 23.83 μW의 저전력 특성을 만족하였다. 제작된 CMCP 회로를 통해 최대 20 VPP의 60 Hz 공통-모드 간섭을 일정한 공통-모드 동작 범위 내로 제어할 수 있음을 검증하였다. 실제 심전도 신호를 측정한 결과 제작된 회로가 심전도 측정에 적절함을 입증하였다.

향후, 전극 및 회로를 집적하여 소형화된 심전도 신호 측정 모듈을 제작하여 제작된 회로를 통한 측정을 통해 휴대성이나 장시간 측정에 적합한 가에 대한 연구의 추가적인 진행이 필요함으로 보인다.

Acknowledgments

이 연구는 충남대학교 학술연구비에 의해 지원되었음.

REFERENCES

-

D. De Bacquer, G. De Backer, M. Kornitzer, and H. Blackburn, “Prognostic value of ECG findings for total, cardiovascular disease, and coronary heart disease death in men and women”, Heart, Vol. 80, No. 6, pp. 570-577, 1998.

[https://doi.org/10.1136/hrt.80.6.570]

-

A. Bansal and R. Joshi, “Portable out-of-hospital electrocardiography: A review of current technologies”, Journal of arrhythmia, Vol. 34, No. 2, pp. 129-138, 2018.

[https://doi.org/10.1002/joa3.12035]

-

B. B. Winter and J. G. Webster, “Driven-right-leg circuit design”, IEEE Trans. Biomed. Eng., Vol. BME-30, No. 1, pp. 62-66, 1983.

[https://doi.org/10.1109/TBME.1983.325168]

- A. Wong, K.-P. Pun, Y.-T. Zhang, and C.-S. Choy, “An ECG measurement IC using driven-right-leg circuit”, proc. of 2006 IEEE Int. Symp. Circuits. Syst. (ISCAS), pp. 345-348, Kos, Greece, 2016.

-

N. Koo and S. Cho, “A 24.8-μW biopotential amplifier tolerant to 15-VPP Common-mode interference for two-electrode ECG recording in 180-nm CMOS”, IEEE J. SolidState Circuits, Vol. 56, No. 2, pp. 591-600, 2020.

[https://doi.org/10.1109/JSSC.2020.3005768]

-

N. Koo and S. Cho, “22.4 A 27.8μW Biopotential Amplifier Tolerant to 30Vpp Common-Mode Interference for Two-Electrode ECG Recording in 0.18μm CMOS”, Proc. of 2019 IEEE Int. Solid- State Circuits Conf. - (ISSCC), pp. 366-368, San Francisco, USA, 2019.

[https://doi.org/10.1109/ISSCC.2019.8662373]

-

H. Kim, K. Han, J. Kim, D. You, H. Heo, Y. Kwon, C.-Y. Kim, H.-D. Lee, and H. Ko, “Chopper-Stabilized Low-Noise Multipath Operational Amplifier with Dual Ripple Rejection Loops”, IEEE Trans. Circuits. Syst. II: Express Briefs, Vol. 67, No. 11, pp. 2427-2431, 2020.

[https://doi.org/10.1109/TCSII.2020.2977664]

-

Q. Fan, F. Sebastiano, H. Huijsing, and K. Makinwa, “A 1.8 μW 1μV-offset capacitively-coupled chopper instrumentation amplifier in 65nm CMOS”, Proc. of 2010 Proc. ESSCIRC, pp. 170-173, Seville, Spain, 2010.

[https://doi.org/10.1109/ESSCIRC.2010.5619902]

-

Q. Fan and K. Makinwa, “Capacitively-coupled Chopper Instrumentation Amplifiers: An Overview”, Proc. of 2018 IEEE SENSORS, pp. 1-4, New Delhi, India, 2018.

[https://doi.org/10.1109/ICSENS.2018.8589958]

-

K. Nam, H. Kim, Y. Kwon, G. Choi, T. Kim, C. Kim, D. Cho, J. Lee, and H. Ko, “A Four-Channel Low-noise readout IC for air flow measurement using hot wire anemometer in 0.18 μm CMOS technology”, Sensors, Vol. 21, No. 14, pp. 4694(1)-4694(16), 2021.

[https://doi.org/10.3390/s21144694]

- R. Wu, K. A. A. Makinwa, and J. H. Huijsing, “The design of a chopped current-feedback instrumentation amplifier”, Proc. of 2008 IEEE Int. Symp. Circuits. Syst. (ISCAS), pp. 2466-2469, Seattle, USA, 2008.

-

R. Wu, K. A. A. Makinwa, and J. H. Huijsing, “A chopper current-feedback instrumentation amplifier with a 1 mHz 1/f noise corner and an AC-coupled ripple reduction loop”, IEEE J. Solid-State Circuits, Vol. 44, No. 12, pp. 3232-3243, 2009.

[https://doi.org/10.1109/JSSC.2009.2032710]

-

H. Kim, S. Kim, N. Van Helleputte, A. Artes, M. Konijnenburg, J. Huisken, C. Van Hoof, and R. F. Yazicioglu, “A configurable and low-power mixed signal SoC for portable ECG monitoring applications”, IEEE trans. Biomed. Circuits. Syst., Vol. 8, No. 2, pp. 257-267, 2013.

[https://doi.org/10.1109/TBCAS.2013.2260159]

-

Y. M. Chi, T. -P. Jung, and G. Cauwenberghs, “Dry-Contact and Noncontact Biopotential Electrodes: Methodological Review”, in IEEE Rev. Biomed. Eng., Vol. 3, pp. 106-119, 2010.

[https://doi.org/10.1109/RBME.2010.2084078]

-

M. Chen, I. D. Castro, Q. Lin, T. Torfs, F. Tavernier, C. Van Hoof, and N. Van Helleputte, “A 400GΩ Input-Impedance, 220MVpp Linear-Input-Range, 2.8Vpp CM-Interference-Tolerant Active Electrode for Non-Contact Capacitively Coupled ECG Acquisition”, Proc. of 2018 IEEE Symp. VLSI Circuits, pp. 129-130, Honolulu, USA, 2018.

[https://doi.org/10.1109/VLSIC.2018.8502270]

- X. Zhou, Q. Li, S. Kilsgaard, F. Moradi, S. L. Kappel, and P. Kidmose, “A wearable ear-EEG recording system based on dry-contact active electrodes”, Proc. of 2016 IEEE Symp. VLSI Circuits (VLSI-Circuits), pp. 1-2, Honolulu, USA, 2016.