Low-Power CMOS image sensor with multi-column-parallel SAR ADC

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(https://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

This work presents a low-power CMOS image sensor (CIS) with a multi-column-parallel (MCP) readout structure while focusing on improving its performance compared to previous works. A delta readout scheme that utilizes the image characteristics is optimized for the MCP readout structure. By simply alternating the MCP readout direction for each row selection, additional memory for the row-to-row delta readout is not required, resulting in a reduced area of occupation compared to the previous work. In addition, the bias current of a pre-amplifier in a successive approximate register (SAR) analog-to-digital converter (ADC) changes according to the operating period to improve the power efficiency. The prototype CIS chip was fabricated using a 0.18-μm CMOS process. A 160 × 120 pixel array with 4.4 μm pitch was implemented with a 10-bit SAR ADC. The prototype CIS demonstrated a frame rate of 120 fps with a total power consumption of 1.92 mW.

Keywords:

CMOS image sensor (CIS), Successive approximate register (SAR), Analog-to-digital converter (ADC), Image property, Delta readout scheme1. INTRODUCTION

Currently, customer demands for CMOS image sensor (CIS)-based applications are growing rapidly [1,2]. In particular, multiple CISs are mounted as electronic eyes on personalized portable devices such as mobile phones and healthcare applications. Because such electronic devices are mostly powered by batteries, maintaining low power consumption has become an important design issue for imaging sensor systems.

For analog-to-digital (A/D) conversion of signals, there are various types of readout analog-to-digital converters (ADCs): single-slope (SS) ADC, sigma-delta (Σ-Δ) ADC, successive approximate register (SAR) ADC, and cyclic (CY) ADC [3]-[6]. Among them, the SAR ADC has been in the spotlight for low-power readout because it does not consume static power. However, its capacitive digital-to-analog converter (C-DAC) for generating a full A/D reference requires a large area, making it difficult to design a layout in a narrow column pitch. Moreover, because the pixel pitch becomes smaller for high pixel resolution, the same problem is encountered in other types of column-parallel (CP) readout ADCs. Here, the pixel pitch is equal to the column pitch in the CP readout structure. To overcome this disadvantage, multi-column-parallel (MCP) readout structures in which one readout ADC covers several columns have been reported [7-9].

Recently, in addition to the studies on traditional circuit techniques for low-power design, various studies [8-11] utilizing the characteristics of the input signal have been reported to obtain further performance improvement. In a previous work [8], based on the image properties, a delta readout scheme that reads only the signal difference between two adjacent pixels (Δpx) has been proposed for a power-efficient readout with SAR ADCs. After completing the A/D conversion for the previous pixel by utilizing its most significant bits (MSBs) MSB information, the C-DAC of the SAR ADC is not fully reset; only the remaining least signal bits (LSBs) are reset. MSBs are memorized and then re-switched in C-DAC for the next A/D conversion. Because the MSB information from the previous pixel is highly correlated with a selected pixel, the number of conversion steps is effectively reduced, resulting in a low-power readout.

In this work, with the same motivations as previous studies, we propose a more optimized delta readout algorithm for rolling-shutter readout CISs adopting the MCP readout structure. Compared to prior studies [8,9], this work considers the row-to-row correlation when changing the row to readout the pixel information (as in rolling shutter readout mechanism). Furthermore, depending on the readout timings, the power saving effect is maximized by effectively controlling the static bias current of a pre-amplifier in the proposed SAR ADC.

The remainder of this paper is organized as follows: Section 2 describes the circuit design issues of the proposed low-power imaging sensors with an advanced delta readout scheme. The measured results and discussions about the proposed CIS are presented in Section 3, followed by the conclusion in Section 4.

2. PROPOSED CMOS IMAGE SENSOR

2.1 Multi-column-parallel readout structure

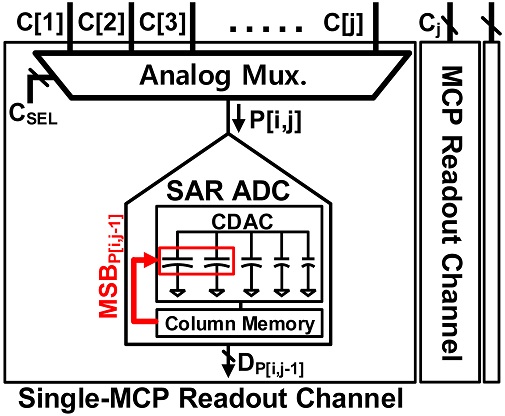

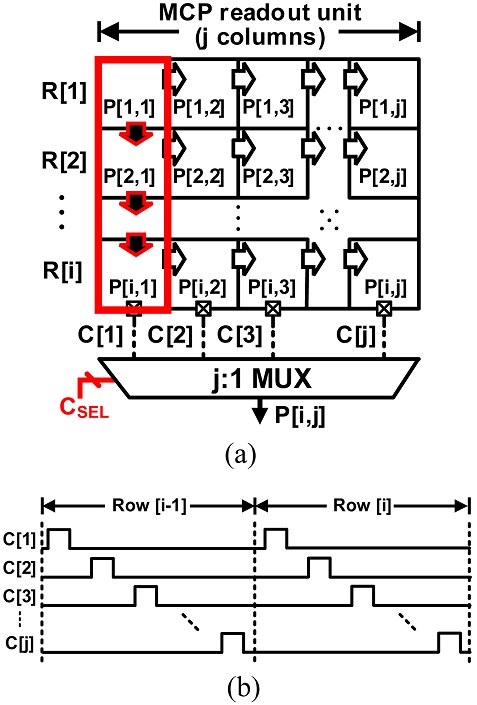

Fig. 1 shows a simplified schematic of the MCP readout structure [8,12], which uses one readout ADC per multiple columns. The pixel information P[i,j] in each MCP unit of a selected row is sequentially input through the analog MUX to each readout ADC from C[1] to C[j], where i represents the i-th row, and j represents the j-th columns. In this work, the proposed SAR ADC is based on the delta readout scheme similar to that in [8] in which MSBs are copied from the A/D conversion result of the previous pixel (MSBP[i,j-1]), and only the remaining LSBs are resolved for the selected pixel.

2.2 Delta Readout Scheme Optimized in MCP readout

The sequence of the delta readout scheme in the MCP readout unit is shown in Fig. 2. There are two readout directions of the column-to-column (P[1,1] → P[1,j]) and the row-to-row (P[1,1] → P[i,1]) readout for copying MSBs utilizing the correlation between adjacent pixels. When applying the delta readout in the row-to-row direction, additional memory is required to copy MSBs from the first pixel in the previous row. Although the MCP readout structure is more advantageous in terms of layout design than the CP readout structure, minimizing its area of occupation is still necessary for noise performance and operating speed optimization [7,12]. This issue can be solved by further considering the MCP readout characteristics.

(a) Explanation of the previously studied delta readout scheme in the row-to-row direction, (b) its MCP readout timing diagram.

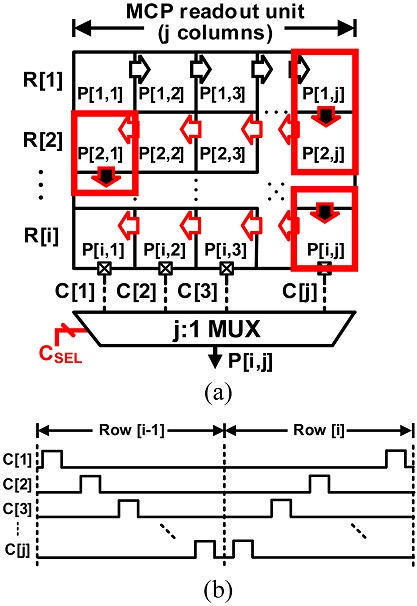

Fig. 3 shows the modified MCP readout direction for the proposed CIS. It is optimized to utilize the correlation between adjacent pixels in the MCP readout structure. Unlike in Fig. 2, each time a row is selected for readout, the analog MUX in the MCP unit changes the selection direction for columns: from C[1] to C[j] in odd rows and from C[j] to C[1] in even rows. In this case, because the delta readout can be applied from P[i-1,j] to P[i,j], no additional memory is required to store the MSB information of P[i,1] in every row.

(a) Modified MCP readout direction for optimizing row-to-row delta readout, (b) its MCP readout timing diagram.

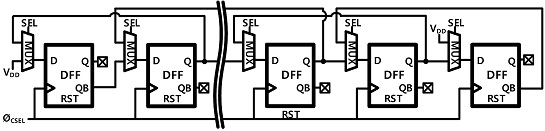

A simplified schematic of the controller of the analog MUX is shown in Fig. 4. It is based on the conventional shift register with additional MUXs to change the logical shifting direction depending on the control signal of ‘SEL’. The control signals of the analog MUX are globally fed into all MCP readout channels without affecting the circuit performance.

2.3 Bias current controlled readout scheme

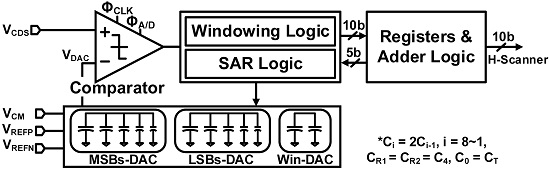

Fig. 5 shows a simplified 10-bit SAR ADC applying the delta readout scheme. Similar to [8], the binary-weighted C-DAC is composed of an MSBs-DAC, an LSBs-DAC, and a win-DAC. In this study, a pre-amplifier based on an operational transconductance amplifier (OTA) [13] is used in the comparator as a typical two-stage topology. During A/D conversion, the pre-amplifier minimizes kickback noise and coupling noise in the columns of the MCP unit. However, this leads to high power consumption owing to the use of constant current during the entire CIS operation.

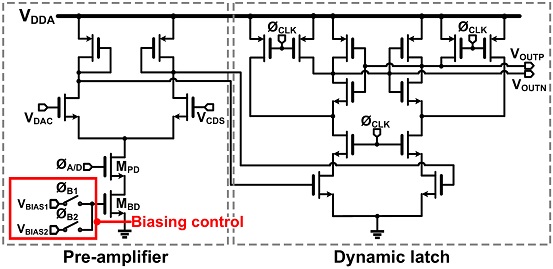

Fig. 6 shows a simplified schematic of the designed two-stage comparator of the pre-amplifier stage and the dynamic latch. To minimize the current dissipation, the bias voltage of the MBD in the pre-amplifier is controlled depending on the operation period. The 1-row conversion period (TROW) is composed of the pixel reset ØRST and pixel readout ØSIG period (TB1) and A/D conversion period (TB2). Because a high current is required only during TB2, the proper bias voltage (VBAIS2) is supplied to the MBD to ensure the speed and voltage gain of the pre-amplifier. Then, during TB1, its bias current is lowered by supplying VBAIS1, which changes only the static operating point of the pre-amplifier. This results in a reduction of power consumption. The average current (Iavg) of the pre-amplifier can be calculated by

| (1) |

where IB1 and IB2 are the currents of the pre-amplifier during TB1 and TB2, respectively. In this work, a bias current of approximately 2.55 μA was used during TB2 to maximize the performance of the comparator, and in the rest of the operation period TB1, a bias current of approximately 1.55 μA was used to reduce the power consumption.

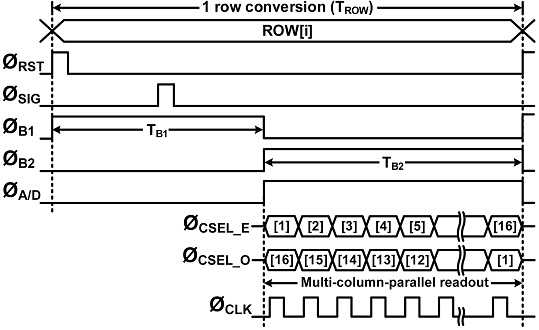

The overall timing diagram is shown in Fig. 7. During ØA/D, all columns in each MCP unit are sequentially selected, and the A/D conversion is performed. The bias voltages of VBAIS1 and VBAIS2 for the pre-amplifier are supplied according to the operating period. The analog MUXs are controlled by ØCSEL, and it changes the readout direction depending on the even row (ØCSEL_E) and odd row (ØCSEL_O).

3. MEASUREMENT RESULTS

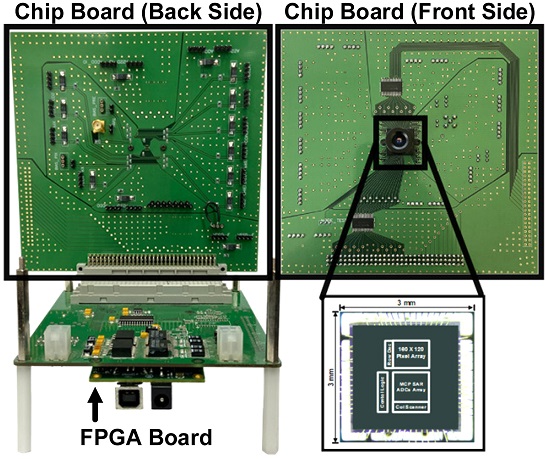

Fig. 8 shows a photograph of the testing CIS board with a microphotograph of the prototype chip. The chip was fabricated using a 0.18-μm CMOS process. A 160 × 120 pixel array with 4.4 μm pitch was implemented with 10 MCP readout channels, in which one SAR ADC covers 16 columns of pixels. The testing CIS board comprises a chip board and a field-programmable gate array (FPGA) board. The fabricated CIS chip was bonded to the chip board. To verify the performance of the prototype CIS, various types of control signals were generated by an external FPGA and supplied to the chip board by the FPGA board. The output codes of the chip board were transmitted to the PC through the USB interface and processed using a software program to display the real-time imaging on the screen. The capturing software program with various verification functions was customized using MATLAB programming.

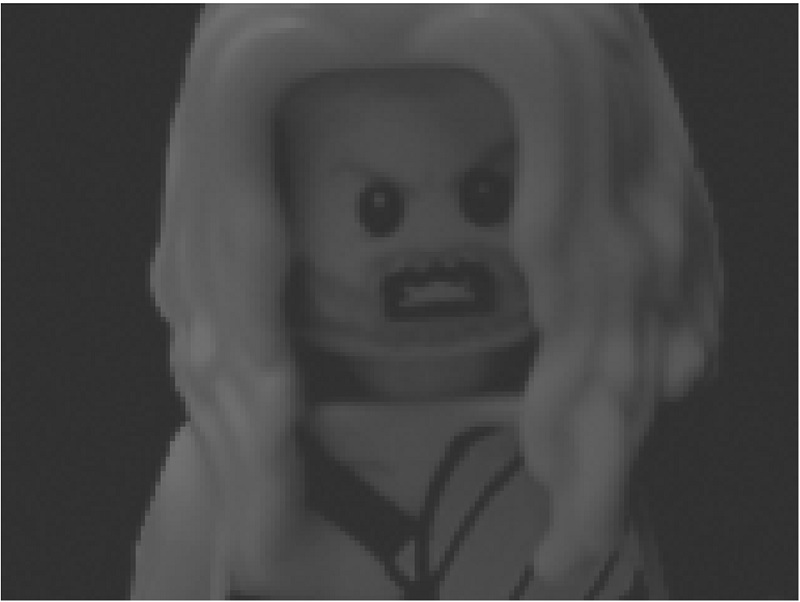

A sample image captured by the prototype CIS is shown in Fig. 9. The prototype CIS demonstrated a frame rate of 120 frame per second (fps) with a total power consumption of 1.92 mW. In the dark illumination condition, as in [14], 100 frames were captured to obtain the standard deviation of noise, resulting in 0.47 LSBrms, corresponding to 413.1 μVrms. The 10-bit SAR ADC has the full input range of approximately 0.9 V with 1-LSB of 880 μV. A fixed-pattern noise from the MCP readout pattern was removed using off-chip digital calibration [8,9]. The pixel rate of the prototype CIS is approximately 2.3 mega pixel per second (Mp/s). With the proposed biasing control method, compared to the conventional MCP readout, a power saving effect of 10.6% was confirmed in this study. The measured performance of the prototype CIS is summarized in Table 1.

The figure of merit (FoM) in terms of power efficiency and noise performance [15,16] is calculated as

| (2) |

From this, the developed CIS obtained an FoM of 344.3 μV·nJ. Table 2 shows the performance comparison with other works based on the 3T-APS pixel array. In terms of noise performances, it was confirmed that coupling noises between neighboring columns occurred owing to insufficient shielding. With further addition of the layout shielding pattern, the random noise will be reduced, resulting in further improved FoM. The measured performance of the prototype CIS is summarized in Table 1.

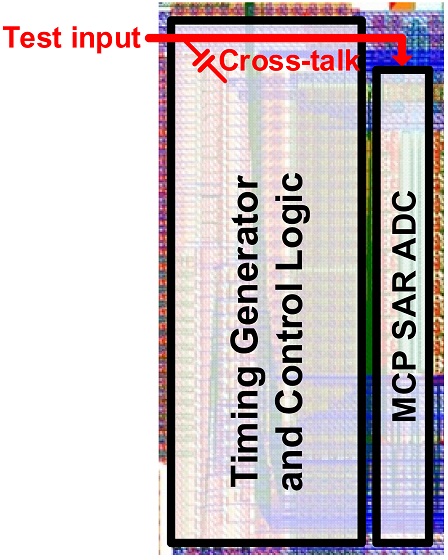

One of the layout issues in this work is that the input of the test ADC is laid without considering shielding across the global digital logic and timing generator, as shown in Fig. 10. Therefore, it is difficult to evaluate the performance of the designed ADC alone, such as differential non-linearity (DNL), integral non-linearity (INL), and readout noise. This problem is expected to be solved sufficiently by modifying the layout pattern.

4. CONCLUSIONS

In this study, we proposed a delta readout SAR ADC optimized in the MCP readout structure. By alternating the MCP readout direction between the even and odd rows, additional memory for the row-to-row delta readout was not required, resulting in a reduced area of occupation. In addition, by applying different bias currents of a pre-amplifier according to the operating period, the power efficiency was improved compared to the previous work. This work is meaningful in that it overcomes the shortcomings of previous studies.

Acknowledgments

This study was supported by 2021 Research Grant from Kangwon National University. This work was also supported by a National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. 2020R1I1A3074020). The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

REFERENCES

- http://www.epnc.co.kr/news/articleView.html?idxno=75952/, (retrieved on Apr. 21, 2021).

-

M. Amjad, M. H. Rehmani, and S. Mao, “Wireless multimedia cognitive radio networks: A comprehensive survey”, IEEE Commun. Surveys Tut., Vol. 20, No. 2, pp. 1056–1103, 2018.

[https://doi.org/10.1109/COMST.2018.2794358]

-

H. Kim, “11-bit Column-Parallel Single-Slope ADC With First-Step Half-Reference Ramping Scheme for High-Speed CMOS Image Sensors”, Journal of Solid-State Circuits, Vol. 56, No. 7, pp. 2132-2141, 2021.

[https://doi.org/10.1109/JSSC.2021.3059909]

-

S. Sukegawa, T. Umebayashi, T.Nakajima, H. Kawanobe, K. Koseki, I. Hirota, T. Haruta, M. Kasai, K. Fukumoto, T. Wakano, K. Inoue, H. Takahashi, T. Nagano, Y. Nitta, T. Hirayama, and N. Fukushima, “A 1/4-inch 8 Mpixel back-illuminated stacked CMOS image sensor”, IEEE Conf. International Solid-State Circuits, pp. 484–485, San Francisco, USA, 2013.

[https://doi.org/10.1109/ISSCC.2013.6487825]

-

T. Arai, T.Yasue, K. Kitamura, H. Shimamoto, T. Kosugi, S. Jun, S. Aoyama, M. Hsu, Y. Yamashita, H. Sumi, and S. Kawahito, “6.9 A 1.1μm 33Mpixel 240fps 3D-stacked CMOS image sensor with 3-stage cyclic-based analog-to-digital converters”, IEEE Conf. International Solid-State Circuits, pp. 126-128, San Francisco, USA, 2016.

[https://doi.org/10.1109/ISSCC.2016.7417939]

-

C. Okada, K. Uemura, L. Hung, K. Matsuura, T. Moue, D. Yamazaki, K. Kodama, M. Okano, T. Morikawa, K. Yamashita, O. Oka, I. Shvartz, G. Zeituni, A. Benshem, N. Eshel, and Y. Inada, “7.6 A High-Speed Back-Illuminated Stacked CMOS Image Sensor with Column-Parallel kT/C-Cancelling S&H and Delta-Sigma ADC”, IEEE Conf. International Solid-State Circuits, pp.116-118, San Francisco, USA, 2021.

[https://doi.org/10.1109/ISSCC42613.2021.9366024]

- D. Van Blerkom, S. Huang, L. Truong and B. Mansoorian, “Analysis of front-end multiplexing for column parallel image sensors”, in Proc. IEEE International Image Sensor Workshop, pp. 1–4, Pasadena, US, 2011.

-

H. J. Kim, S. I. Hwang, J. W. Kwon, D. H. Jin, B. S. Choi, S. G. Lee, J. H. Park, J. K. Shin, and S. T. Ryu, “A Delta-Readout Scheme for Low-Power CMOS Image Sensors With Multi-Column Parallel SAR ADCs”, Journal of Solid-State Circuits, Vol. 51, No. 10, pp. 2262-2273, 2016.

[https://doi.org/10.1109/JSSC.2016.2581819]

-

H. J. Kim, S. I. Hwang, J. H. Chung, J. H. Park, and S. T. Ryu, “A Dual Imaging Speed-Enhanced CMOS Image Sensor for Real Time Edge Image Extraction”, Journal of Solid-State Circuits, Vol. 52, No. 9, pp. 2488-2497, 2017.

[https://doi.org/10.1109/JSSC.2017.2718665]

-

F. M. Yaul and A. P. Chandrakasan, “11.3 A 10b 0.6nW SAR ADC with data-dependent energy savings using LSB-first successive approximation”, IEEE ISSCC Dig. Tech. papers, pp. 198-199, San Francisco, USA, 2014.

[https://doi.org/10.1109/ISSCC.2014.6757398]

- J. Yang, S. Park, J. Choi, H. Kim, C. Park, S. Ryu, and G. Cho, “A highly noise-immune touch controller using Filtered-Delta-Integration and a charge-interpolation technique for 10.1-inch capacitive touch-screen panels”, IEEE Conf. International Solid-State Circuits, pp. 390-391, San Francisco, USA, 2012.

-

R. Funatsu, S. Huang, T. Yamashita, K. Stevulak, J. Rysinski, D. Estrada, S. Yan, T. Soeno, T. Nakamura, T. Hayashida, H. Shimamoto and B. Mansoorian, “6.2 133 Mpixel 60fps CMOS image sensor with 32-column shared high-speed column-parallel SAR ADCs”, IEEE Conf. International Solid-State Circuits, pp. 112–113, San Francisco, USA, 2015.

[https://doi.org/10.1109/ISSCC.2015.7062951]

-

E. Sanchez-Sinencio, J. Ramirez-Angulo, B. Linares-Barranco and A. Rodriguez-Vazquez, “Operational transconductance amplifier-based nonlinear function syntheses”, Journal of Solid-State Circuits, Vol. 24, pp. 1576-1586, 1989.

[https://doi.org/10.1109/4.44993]

-

M. W. Seo, T. Sawamoto, T. Akahori, T. iida, T. Takasawa, K. Yasutomi, and S. Kawahito, “A low noise wide dynamic range CMOS image sensor with low-noise transistors and 17b column-parallel ADCs”, IEEE Sensors Journal, Vol. 13, No. 8, pp. 2992-2929, 2013.

[https://doi.org/10.1109/JSEN.2013.2264483]

- S. Kawahito, “Column readout circuit design for high speed low noise imaging”, IEEE Conf. International Solid-State Circuits, Image Sensor Forum, San Francisco, USA, 2010.

-

M. Kwon and B. Murmann, “A New Figure of Merit Equation for Analog-to-Digital Converters in CMOS Image Sensors”, IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, Florence, Italy, 2018.

[https://doi.org/10.1109/ISCAS.2018.8351578]

-

D. G. Chen, F. Tang, and A. Bermak, “A Low-Power Pilot-DAC Based Column Parallel 8b SAR ADC With Forward Error Correction for CMOS Image Sensors”, IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 60, No. 10, pp. 2572-2583, 2013.

[https://doi.org/10.1109/TCSI.2013.2244317]

- D. G. Chen, F. Tang, M. Law, X. Zhong, and A. Bermak, “A 64 fJ/step 9-bit SAR ADC Array With Forward Error Correction and Mixed-Signal CDS for CMOS Image Sensors”, IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 61, No. 11, pp. 3085-3093, 2014.