Development of Semiconductor Packaging Technology using Dicing Die Attach Film

This is an Open Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License(https://creativecommons.org/licenses/by-nc/3.0/) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract

Advanced packaging demands are driven by the need for dense integration systems. Consequently, stacked packaging technology has been proposed instead of reducing the ultra-fine patterns to secure economic feasibility. This study proposed an effective packaging process technology for semiconductor devices using a 9-inch dicing die attach film (DDAF), wherein the die attach and dicing films were combined. The process involved three steps: tape lamination, dicing, and bonding. Following the grinding of a silicon wafer, the tape lamination process was conducted, and the DDAF was arranged. Subsequently, a silicon wafer attached to the DDAF was separated into dies employing a blade dicing process with a two-step cut. Thereafter, one separated die was bonded with the other die as a substrate at 130 oC for 2 s under a pressure of 2 kgf and the chip was hardened at 120 oC for 30 min under a pressure of 10 kPa to remove air bubbles within the DAF. Finally, a curing process was conducted at 175 oC for 2 h at atmospheric pressure. Upon completing the manufacturing processes, external inspections, cross-sectional analyses, and thermal stability evaluations were conducted to confirm the optimality of the proposed technology for application of the DDAF. In particular, the shear strength test was evaluated to obtain an average of 9,905 Pa from 17 samples. Consequently, a 3D integration packaging process using DDAF is expected to be utilized as an advanced packaging technology with high reliability.

Keywords:

Dicing die attach film, Packaging process, Tape lamination, Dicing, Die1. INTRODUCTION

The increasing demand for reduction in semiconductor size has resulted in the continuous development of new packaging technologies [1]. With increased focus in reduction of die thickness (less than 100 μm) and package miniaturization, stacked die packaging technology has gained importance [2]. Conventional pastes are not suitable for stacked die packages in case of ultra-thin die because they result in paste bleeding, creeping effect at the edge of the chip, and contamination of the bonding pad [3]. Consequently, die attach films (DAFs) have been introduced as an alternative to tackle these problems. Moreover, the advantages of mounting a DAF at the wafer level are well known [4]. Accordingly, research to determine an optimized process for manufacturing a stacked die using a DAF has been steadily progressing [4-6]. Previous studies have found that sidewall chipping (during the dicing process) [4], two-step dicing methods [7-8], and curing temperature [5] were major factors affecting the reliability of stacked packaging. Thus, an optimal process technology suitable for DAF properties must be obtained. Therefore, this study was aimed to propose an optimal die stacking package process technology suitable for DAF properties.

2. EXPERIMENTAL

2.1 Wafer and DDAF Preparation

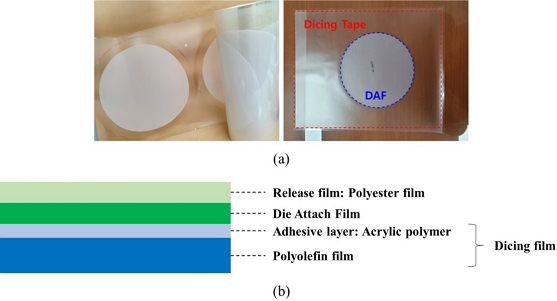

Silicon wafers measuring 200 mm and 725 μm in diameter and thickness were used. As the experiments were focused on the packaging process technology using dicing die attach films (DDAFs), wafer characteristics such as orientation, type, resistivity, and patterned nature were ignored. The silicon wafers were ground to 100 μm using the silicon wafer backside grind process as this was the minimum thickness that could be handled and thus manufactured appropriately. DISCO's DGP8760 equipment was used for the grinding process, wherein a DDAF was produced through the combination of dicing and die attach films. Fig. 1 (a) shows a DDAF with a 9-inch circular die attach film merged into a dicing film in a roll, and the simplified structure of the DDAF is shown in Fig. 1(b). The DDAF comprised dicing and die attach films with a total thickness of approximately 130 μm. Further, the dicing film was approximately 110 μm thick and comprised a polyolefin film and an acrylic polymer acting as an adhesive layer. In contrast, the thickness of the DAF was approximately 20 μm.

2.2 Tape Laminate Process

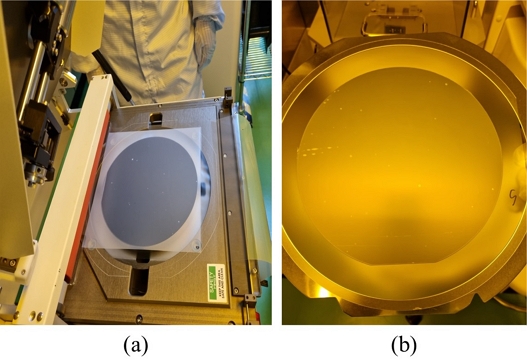

The DDAF was attached to a ground silicon wafer by employing a tape laminate process. The DYNATECH 8-inch manual wafer mount system was used for tape lamination. Following the installation of the manufactured DDAF roll on the equipment, the temperature of the chuck was set to 80 oC to satisfy the DDAF specifications. When the temperature of the chuck reached 80 oC, the ground wafer was placed on the chuck. However, there must be no pores on the wafers when attaching the DDAF; thus. wafers were cleaned of particles and dust beforehand. Subsequently, the DDAF was aligned with the wafer with the tape stretched to a sufficient degree before performing the laminating process. Fig. 2 shows the DDAF lamination process and laminated wafer with the DDAF.

2.3 Dicing Process

The dicing process was conducted to separate the DDAF-laminated wafer into dies based on the blade dicing method conducted using Disco Corp's DAD3350. The dicing process was performed as a two-step cutting method using two types of blades [7-8]. The thickness of the blade wheel, is referred to as kerf. This study used two types of blade kerfs: KH4-1435 (35 μm in length), and KH4-1435 (25 μm in length); both are manufactured by Kodis. In the two-step cut method, first, rough dicing was performed using the 35 μm blade kerf, followed by fine dicing using the 25 μm blade kerf. Further, the DDAF-laminated wafer was cut into half along its depth using the 35 μm blade kerf, and the 25 μm blade kerf was used to cut the remaining thickness of the wafer including the DDAF and a certain depth of the dicing tape. The dicing process was performed at 35,000 rpm and a feed speed of 50 mm/s. In addition, the two-step cut depth differed depending on the thickness of the wafers. Subsequently, the die size was divided into 5 × 5 and 10 × 10 mm 2.

2.4 Die Bonding Process

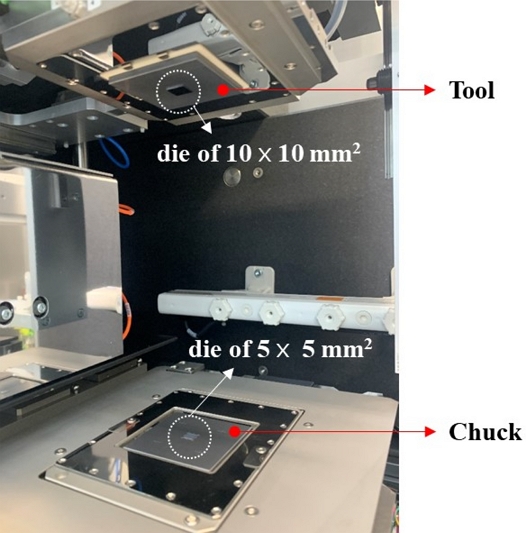

The bonding process employed a die-to-die bonding method (FC150, SET). As shown in Fig. 4, the die placed on the chuck was a 5 × 5 mm2 and 10 × 10 mm2, 100-μm-thick die with the DAF laminated side facing up. The other die was a 10 × 10 mm2, 725-μm-thick die turned over by a flipper and loaded into the tool (specimens created arbitrarily for die-stacked bonding). The bonding conditions were the application of a temperature of 130 oC for 2 s at a pressure of 2 kgf. Following bonding, the dies were placed in a vacuum oven (VAC-101P, Espec) at 120 oC for 30 min at a pressure of 10 kPa to remove air bubbles inside the DAF. Finally, the curing process was conducted at 175 oC for 2 h at atmospheric pressure using the same oven. The thermal curing process is necessary because delamination of the DAF owing to thermal expansion may result in mismatch of values of the interface [5, 9].

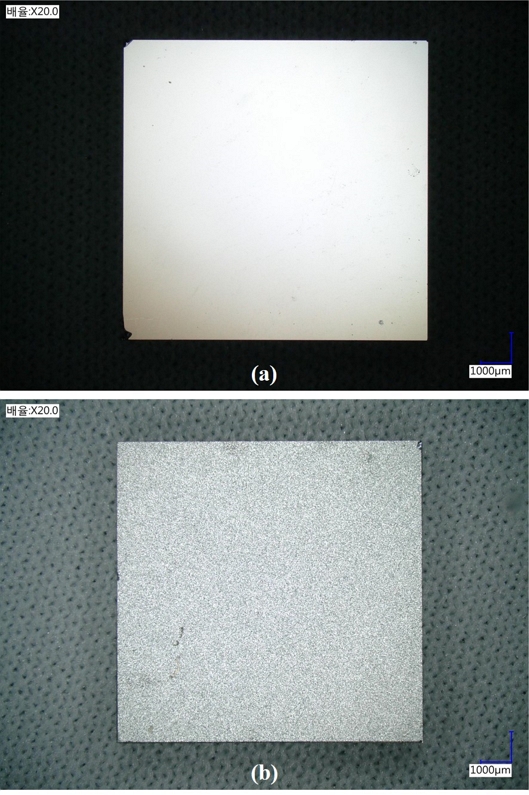

Thus, all processes were finished to complete two bonded chips. One substrate had a silicon size of 10 × 10 mm2, 725-μm-thick, with the upper silicon chip measuring 10 × 10 mm2, 100-μm-thick bonded with DAF (Fig. 5). The other substrate had a silicon size of 10 × 10 mm2, 725-μm-thick, with the upper silicon chip measuring 5 × 5 mm2, 100-μm-thick bonded with DAF (Fig. 6).

3. RESULTS AND DISCUSSIONS

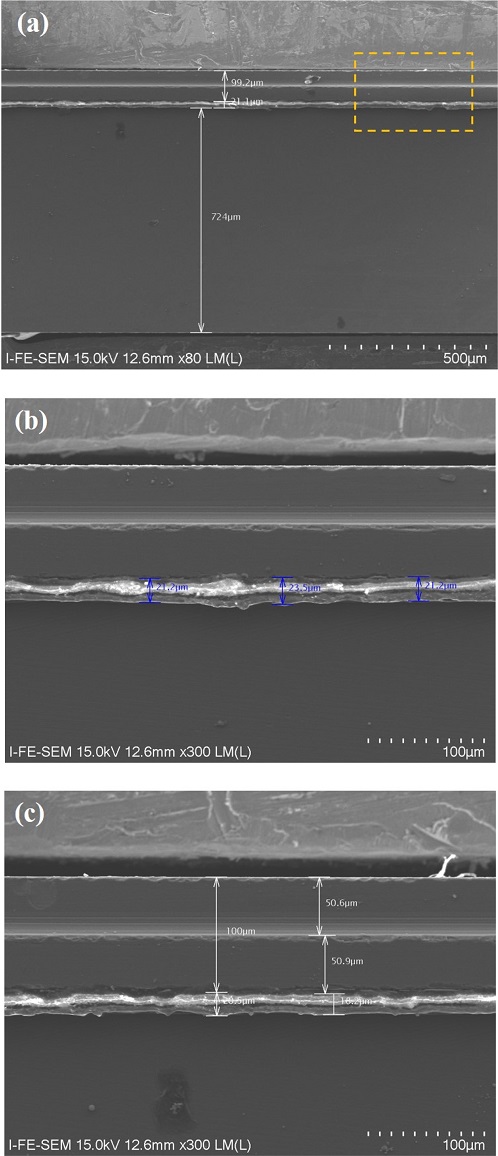

Following the completion of all the processes, the appearance of the chips bonded by the DAF was observed using an optical microscope and FE-SEM. As shown in Fig. 5, no apparent abnormalities in appearance were observed. Fig. 6 shows the observation with FE-SEM. The thicknesses of the lower substrate, DDAF, and upper chip were confirmed to be 725, 20, and 100 μm, respectively (Fig. 6 (a), (b)). Moreover, it is evident that the blade dicing process was performed in two steps at the enlarged die part. Further, a half-cut boundary was observed near 50 μm of the die thickness (Fig. 6 (c)).

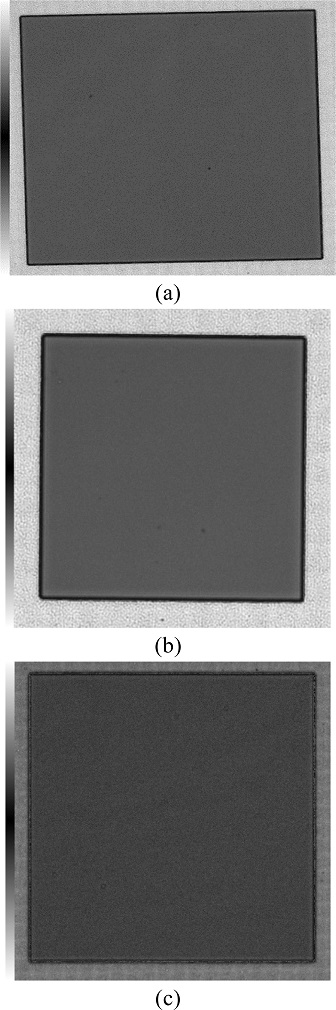

Three experiments were conducted with the chips bonded by the DAF: 1) thermal stability evaluation, 2) constant temperature and humidity evaluation, and 3) shear strength test. First, the thermal stability evaluation was performed by placing the chip with a 100-μm-thick, 10 × 10 mm2 die in an oven at 180° C for 24 h. Subsequently, the adhesion state of the DAF according to heat exposure was analyzed using scanning acoustic microscopy (SAM; Gen6, Sonoscan). Consequently, the constant temperature and humidity evaluation was performed by placing the chip with a 100-μm-thick, 10 × 10 mm2 die in a chamber maintained at 85 °C and 85% relative humidity for 168 h (TH-TG-180, Jeiotech). Following the completion of the bonding process, decompression for defoaming, and final thermal curing process, SAM analysis was performed to confirm the DAF state after conducting the evaluations for thermal stability and constant temperature and humidity. As shown in Fig. 7, all DAF states in the three conditions were confirmed to be intact without adhesive voids. The SAM analysis was performed at a frequency of 150 MHz and a pixel size of 5 μm.

SAM image of DAF state (a) for stacked chips, (b) after the thermal stability evaluation, (c) after the constant temperature and humidity evaluation. All chips are 10 × 10 mm2 in size.

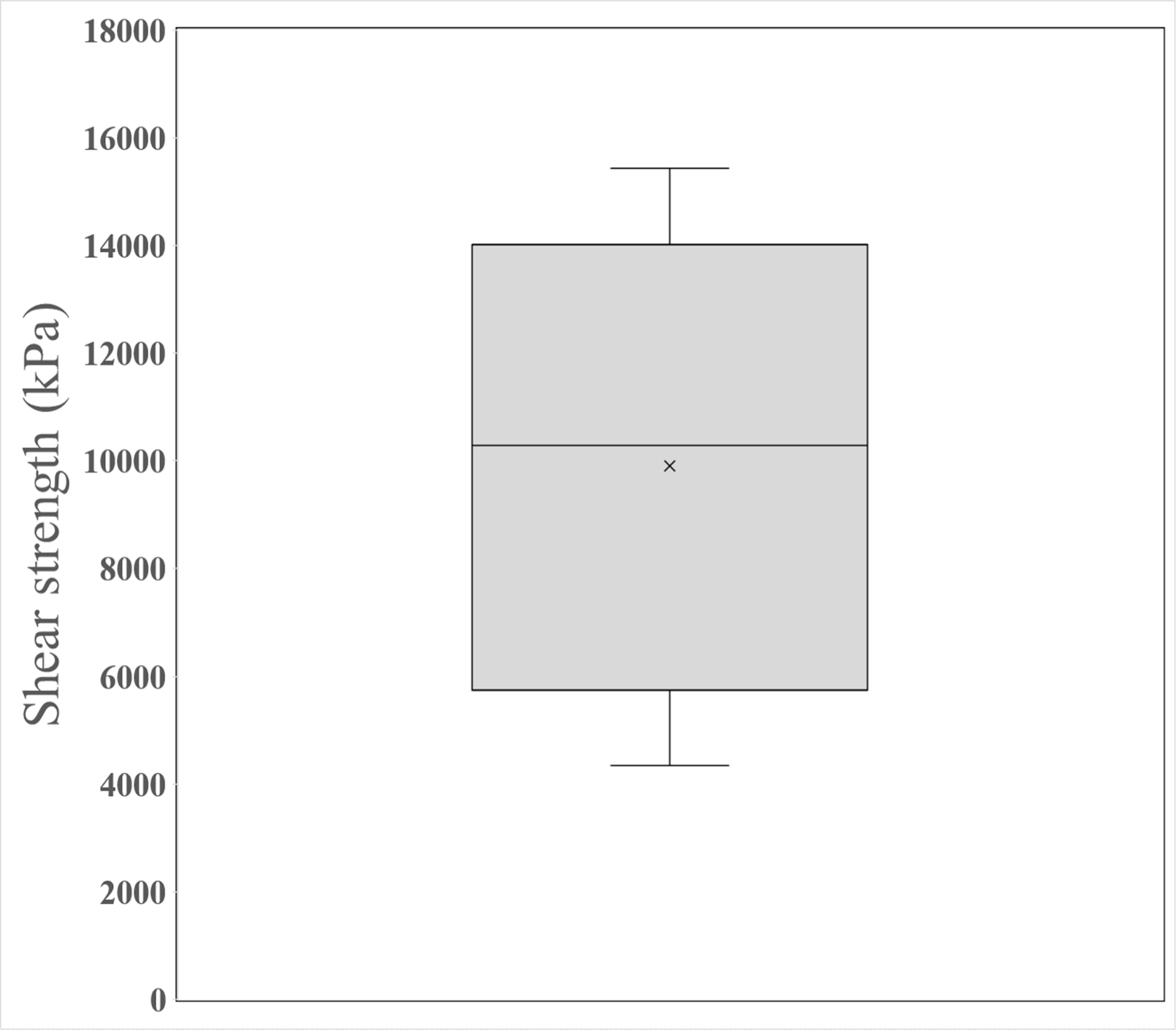

Next, the shear strength test (4000Plus, Nordson dage) was conducted to evaluate the durability during the application of a shear stress. The bonding chip mounted on the chuck was pushed out from the bonding surface between the 725-μm-thick, 10 × 10 mm2 and 100-μm-thick, 5 × 5 mm2 dies at a height and speed of 5 μm and 50 μm/s, respectively, using a tool. Subsequently, shear strength was obtained using the following formula.

- τ = F / A

where τ is the shear stress (kPa), F is the applied force (N), and A is the joint surface area (m2).

The shear strength test evaluated 17 samples to obtain an average of 9,905 Pa, with maximum and minimum values of 15,430 and 4,340 Pa, respectively.

4. CONCLUSIONS

This study proposed a manufacturing process for die-to-die-bonded dummy chips using DDAFs. The analysis of the appearance of the manufactured die revealed no major problems in the appearance and cross-section of the bonded chips. In addition, the results of the analysis following thermal stability evaluation and constant temperature and humidity evaluation confirmed the absence of adhesive voids in the DAF state. Thus, an optimal process for the application of the DDAF was established, and it is expected to be utilized as an efficient semiconductor chip stacking technology.

Acknowledgments

The authors are grateful for support from the Open Innovation Project (CSB2102M001) through the National Nano Fab Center, Republic of Korea. The shear strength test was supported by the QRT.

REFERENCES

-

R. Beica, A. Ivankovic, T. Buisson, S. Kumar, and J. Azemar, “The Growth of Advanced Packaging: An Overview of the Latest Technology Developments, Applications and Market Trends”, Int. Symp. on Microelectron., Vol. 2015, No. 1, pp. 000001-000005, 2015.

[https://doi.org/10.4071/isom-2015-TP11]

-

S. F. Al-Sarawi, D. Abbott, and P. D. Franzon, “A review of 3-D packaging technology”, IEEE Trans. Compon. Packaging Manuf. Technol. B, Vol. 21, No. 1, pp. 2-14, 1998.

[https://doi.org/10.1109/96.659500]

- S. N. Song, H. H. Tan, and P. L. Ong, “Die attach film application in multi die stack package”, 7th Electron. Packaging Technol. Conf., Singapore, 2005.

- A. T. Cheung, “Dicing die attach films for high volume stacked die application”, 56th Electron. Compon. Technol. Conf., San Diego, USA, 2006.

- A. Jalar, M. F. Rosle, and M. A. A. Hamid, “Die attach film performance in 3D QFN stacked die”, WSEAS Trans. Appl. Theor. Mech., Vol. 3, No. 3, pp. 104-113, 2008.

-

M. Teo, S. C. Kheng, and C. Lee, “Process and Material Characterization of Die Attach Film (DAF) for Thin Die Applications”, Int. Conf. on Electron. Mater. Packaging, Hong Kong, China, pp. 1-7, 2006.

[https://doi.org/10.1109/EMAP.2006.4430572]

- H. H. Jiun, I. Ahmad, A. Jalar, and G. Omar, “Alternative double pass dicing method for thin wafer laminated with die attach film”, IEEE Int. Conf. on Semicond. Electron., Kuala Lumpur, Malaysia, 2004.

- C. Paydenkar, A. Poddar, H. Chandra, and S. Harada, “Wafer sawing process characterization for thin die (75micron) applications”, IEEE/CPMT/SEMI 29th Int. Electron. Manuf. Technol. Symp., San Jose, USA, pp. 74-77, 2004.

-

L. L. Mercado, H. Wieser, and T. Hauck, “Multichip package delamination and die fracture analysis”, IEEE Trans. Adv. Packaging, Vol. 26, No. 2, pp. 152-159, 2003.

[https://doi.org/10.1109/TADVP.2003.817335]

-

A. Ivankovic et al, “Fan-in WLP: Market and Technology trends”, Technology and Market Report, Yole Développement, Villeurbanne, 2015.

[https://doi.org/10.4071/isom-2015-TP31]